Other Parts Discussed in Thread: OPA2277, OPA277, INA105, , OPA227, REF102

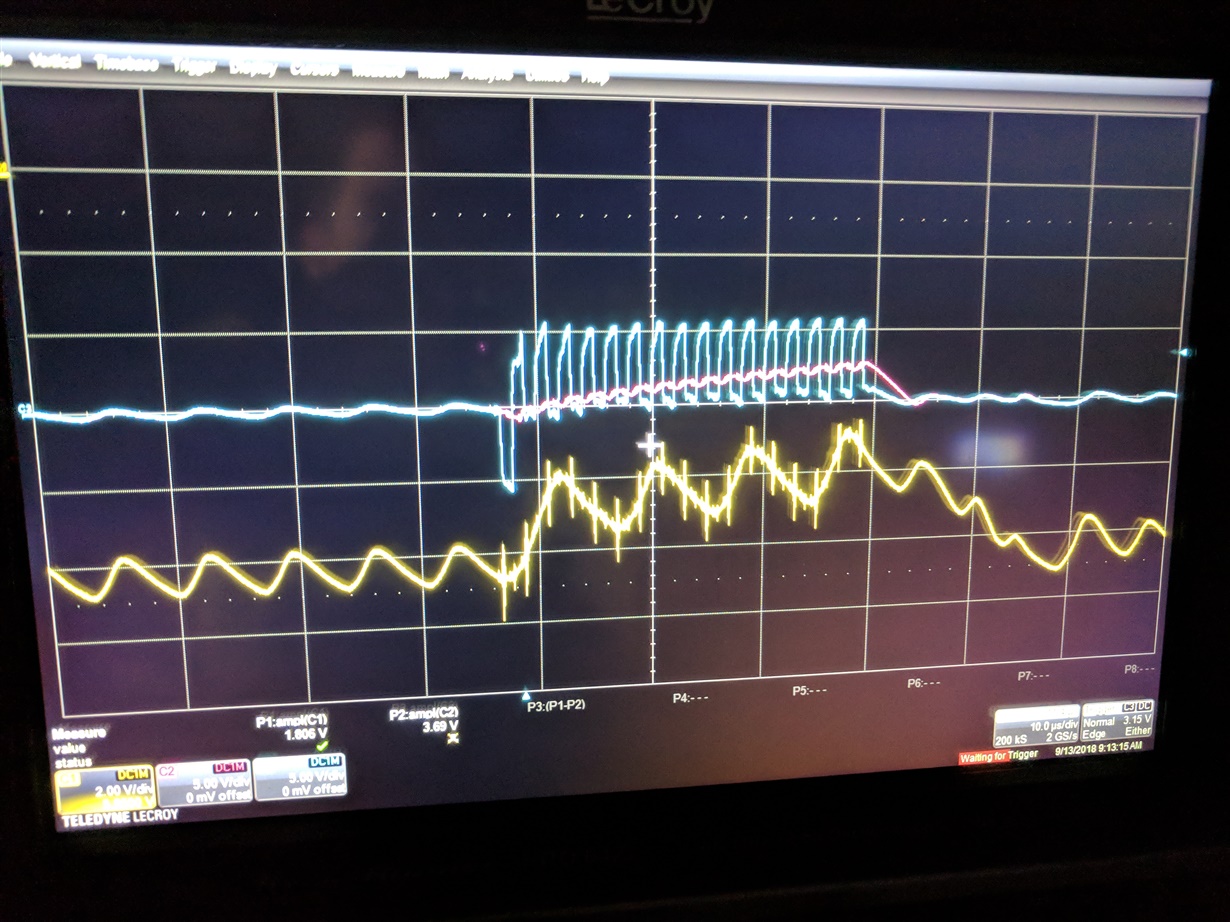

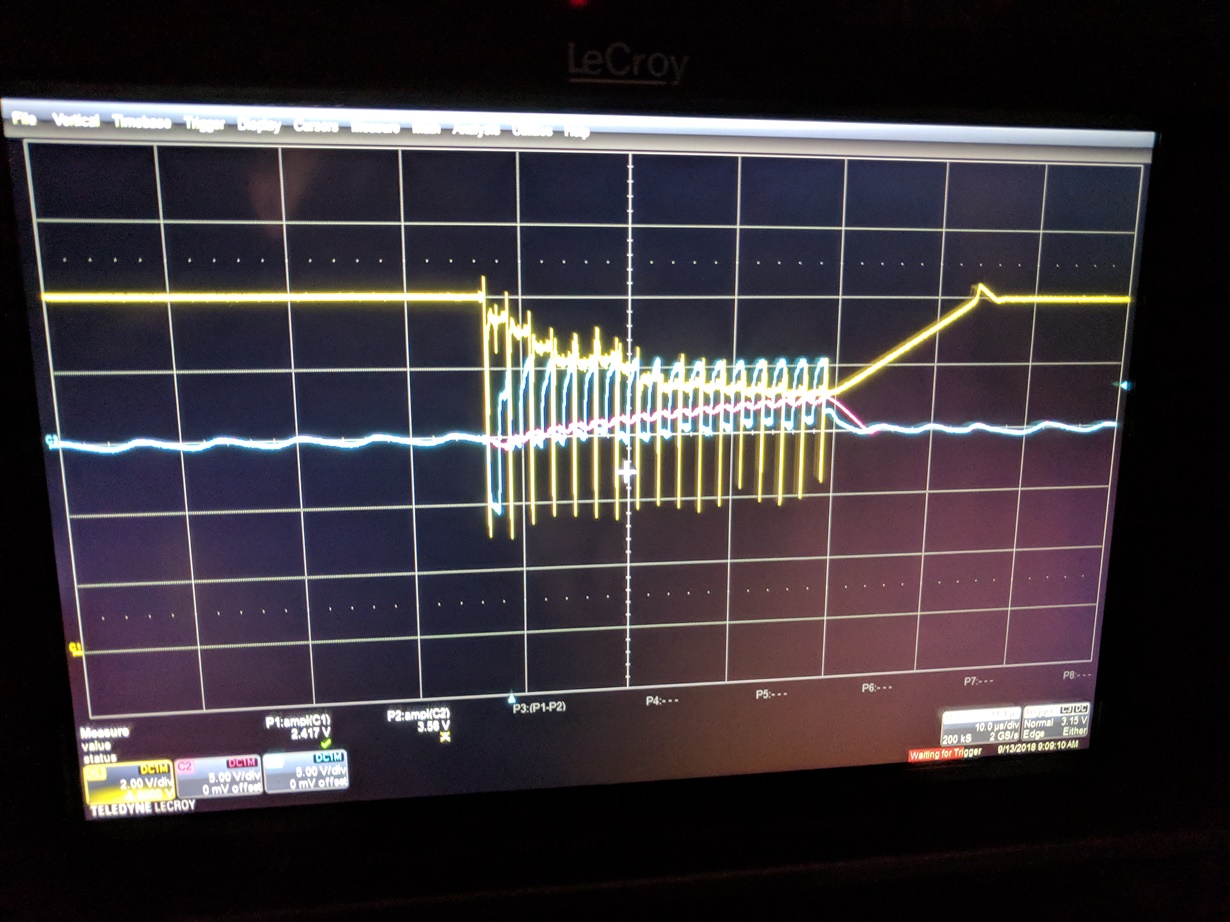

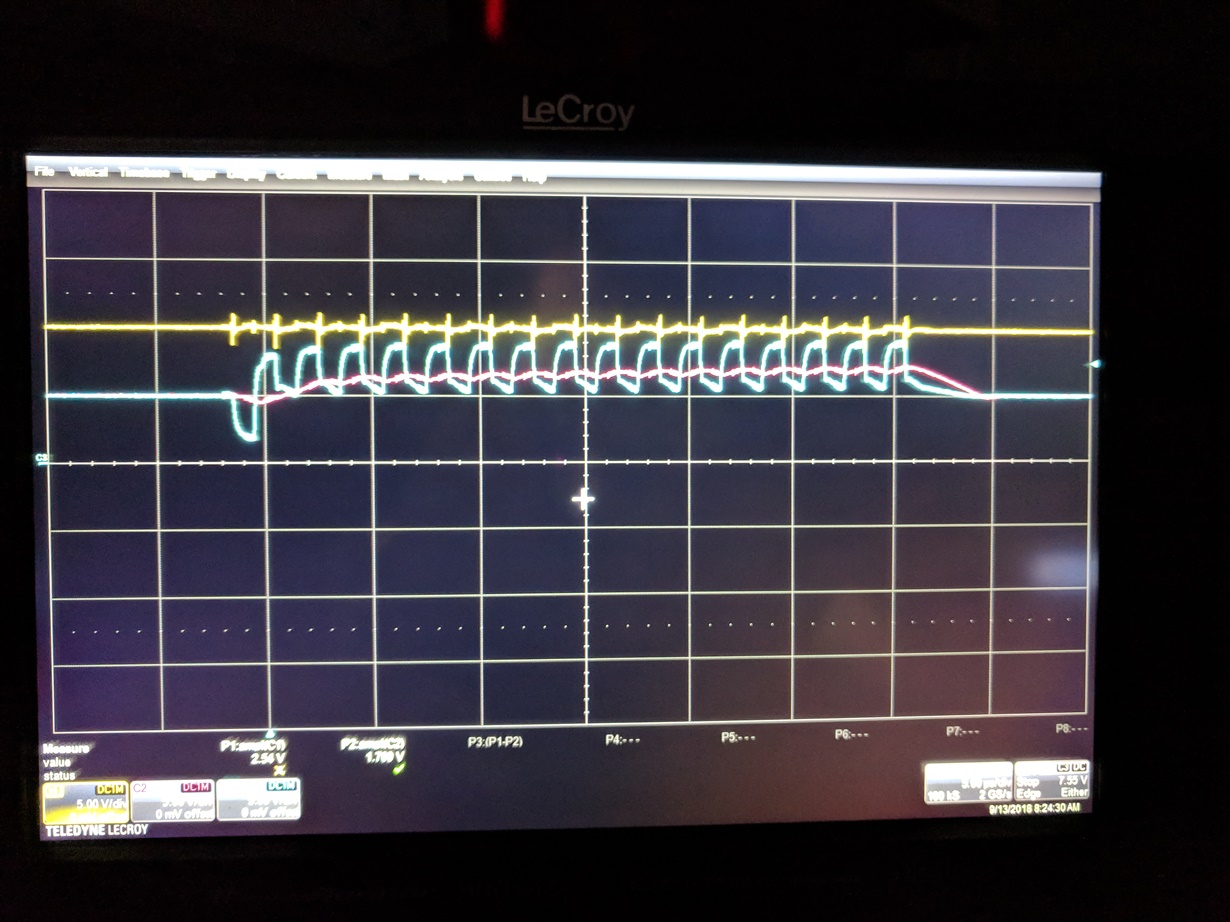

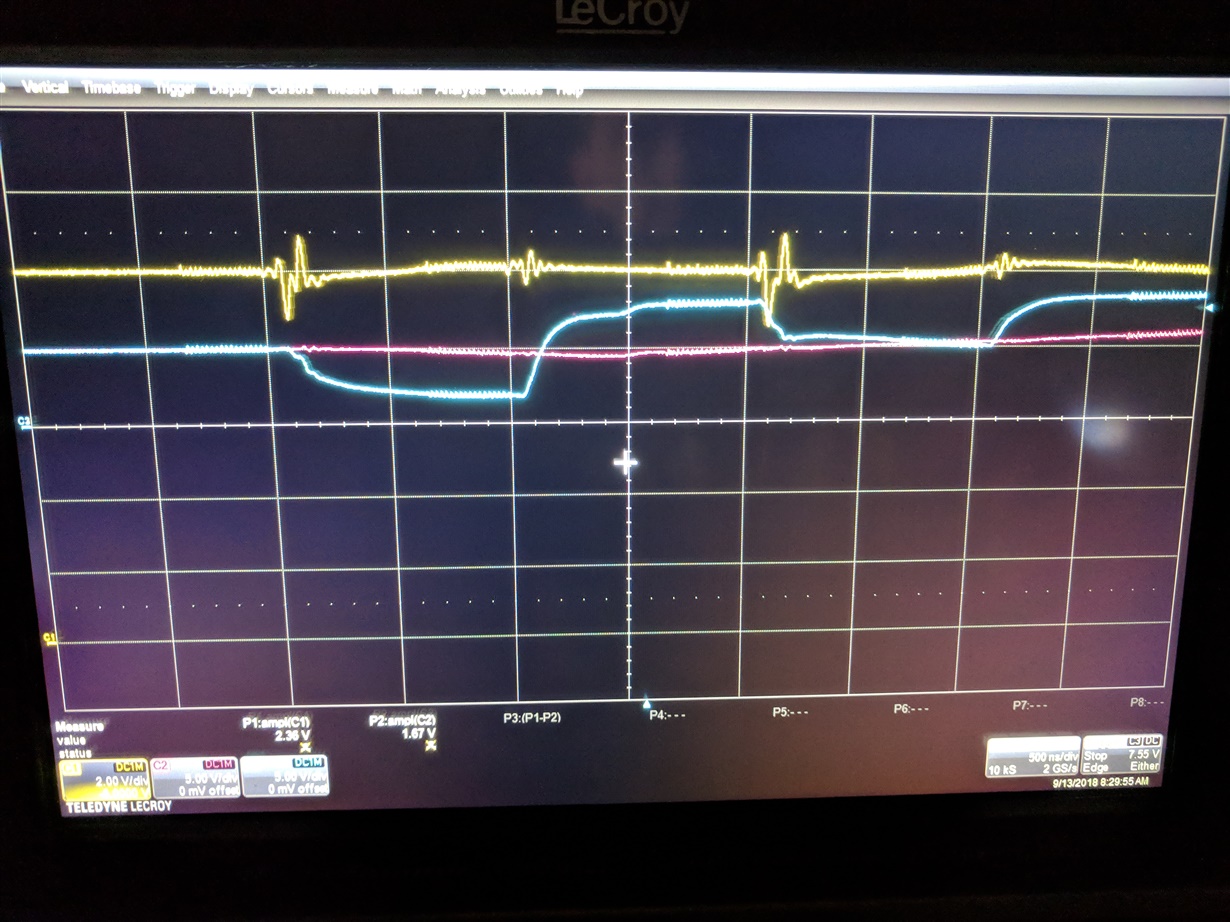

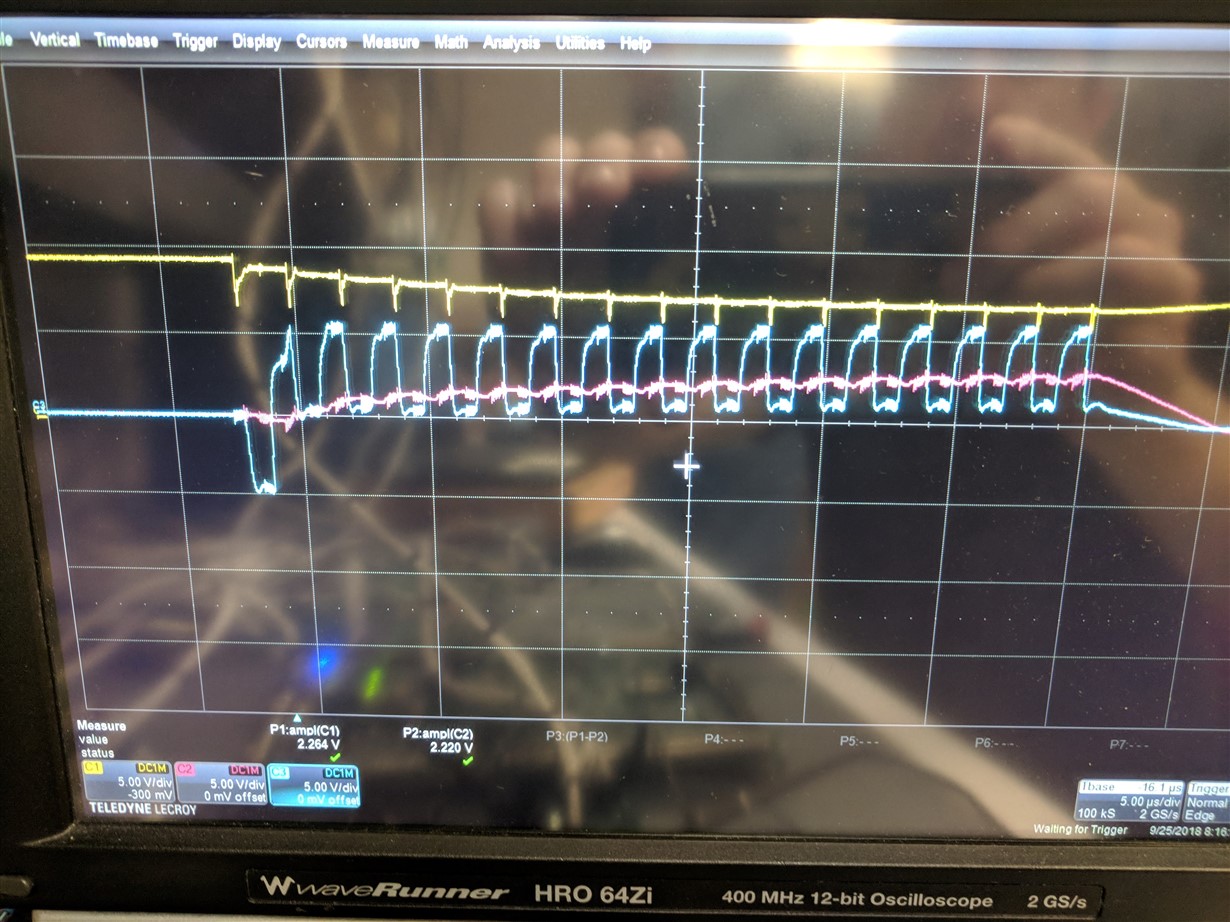

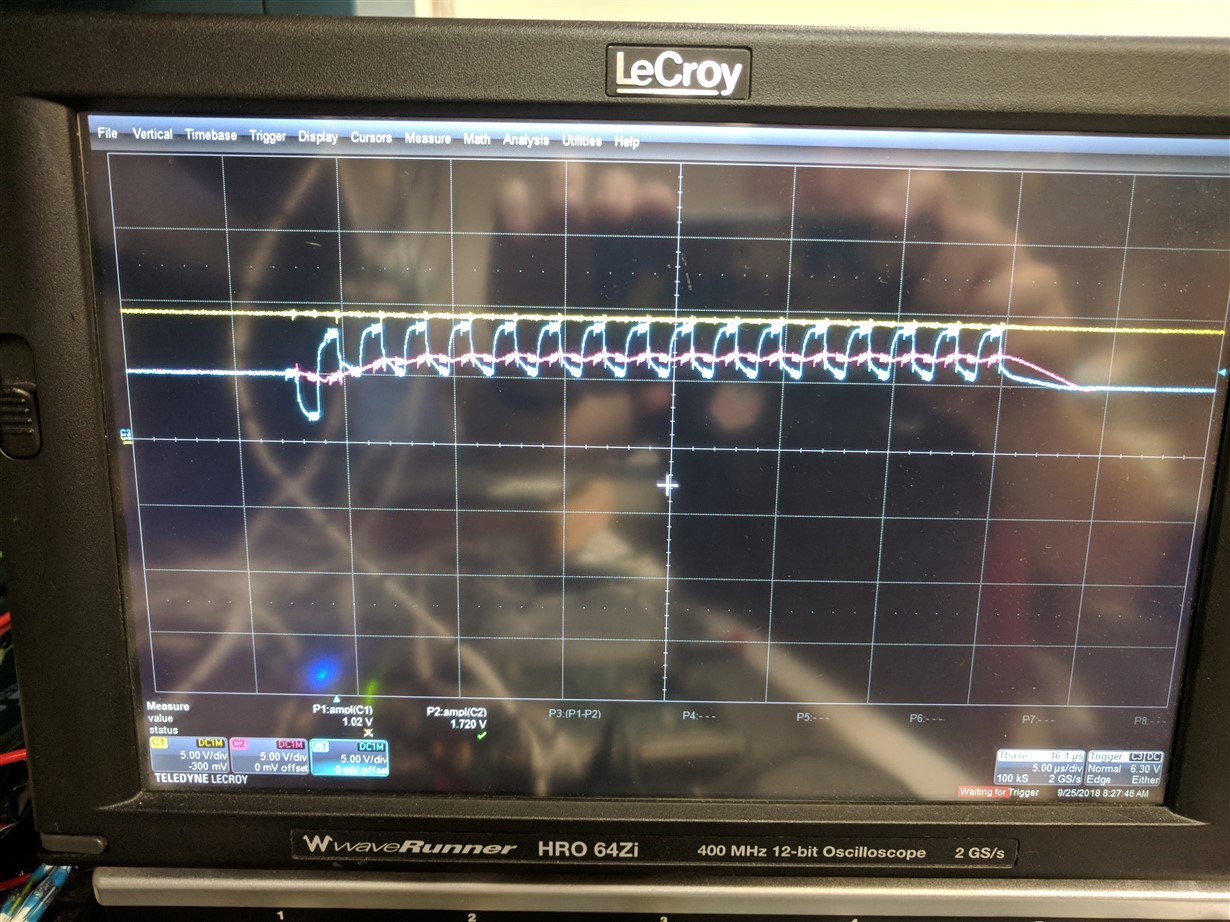

What is the current draw on the VREFH-F with a single 10V Ref when switching at Max Speed and Max code change (full range + to full range -) ?

We are using the OP AMP circuit from the datasheet (OPA2277 without the resistor/capacitor network) but it does not seem to be capable of sourcing the required current.

The current we measure is much higher than the datasheet's Figure 28.