Hello,

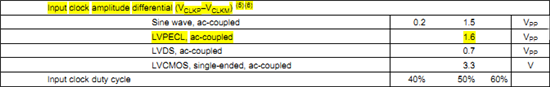

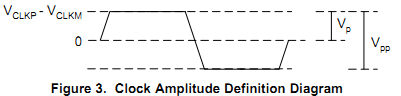

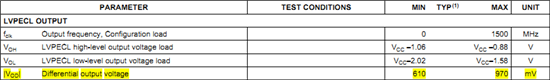

I am using clock synthesizer CDCE62005 to provide clock to ADC ADS62P48. I am attaching a document specifying LVPECL clock output voltage levels of CDCE62005 and LVPECL clock input voltage levels of ADS62P48. Kindly confirm whether this interface will work.

Thanks

Radhika