Dear everyone,

I have a misunderstanding with the DAC 34H84. I am using the TSW30SH84 EVM. My setup is configured as follow:

Signal baseband BW Fs = 307.2MHz

DAC 34H84

Interpolation = 4

Sampling Frequency = 1288.8MHz

Complex Mixer NCO Frequency FNCO = 76.8MHz

LO frequency FLO = 1.9232GHz

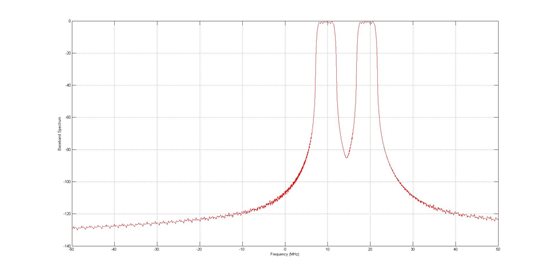

So, I would like to transmit two bands centered at F1=9.6MHz (Fs/32) and 19.2MHz (Fs/16) at baseband level as depicted on figure 1.

By using the GUI, I am able to cancel the IQ imbalance (QMCxxx variable) and the DC offset (Offsetxxx variable).

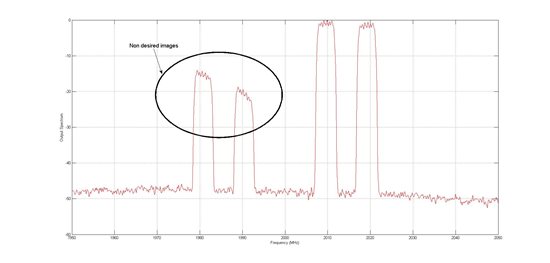

Figure 2 shows the measurement of the RF output from the evaluation board.

On the right of the spectrum, you can observe the two bands that I want to transmit centered at FLO+FNCO+F1=2009.6GHz and FLO+FNCO+F2=2019.2MHz.

However, on the left side of the spectrum, you can observe two not desired “images” centered at FLO+FNCO-F1 and FLO+FNCO-F2.

Of course, I didn’t expect this output so do you know where does this images come from? Is it a bad configuration of the DAC or a problem with images coming from interpolation process?

Thanks a lot for the support.

Christophe