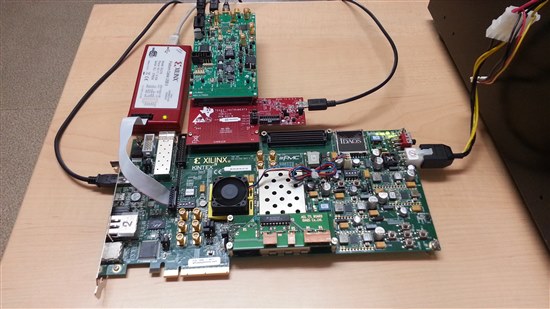

I am using ADC12J4000EVM & TSW14J56.

TSW12J56 has ALTERA FPGA. However, I want to run ADC12J4000EVM with our own Xilinx FPGA board.

Would you please offer the FPGA Referrence Design of TSW14J56, HDL,Firmware...etc?

I try to change the design to Xilinx.

Best Regards,

H Tobe