Dear Sir,

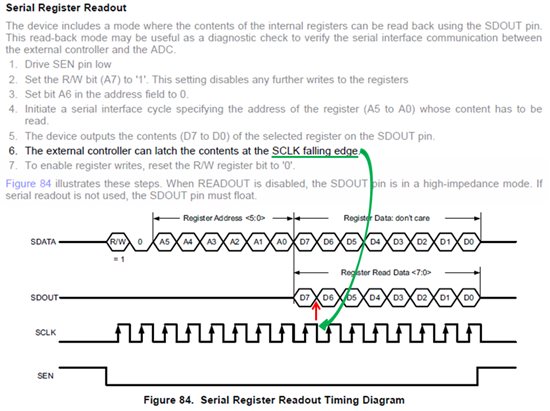

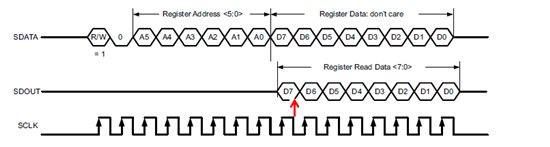

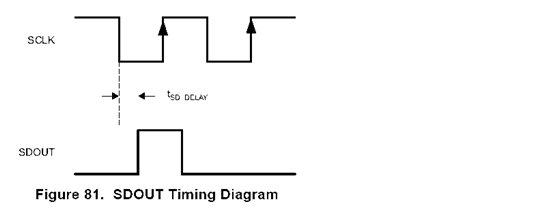

I have a couple of questions about the ADS42LB69 serial interface timing those I could mot find specific data in the data sheet. I am referring page 44 and 45 in the datasheet.

1) I would like to know minimum time to hold SEN high after SEN low to high. In other word how soon SEN can be set to low (active) after SEN was set to high (disable) as a minimum interval time for register access.

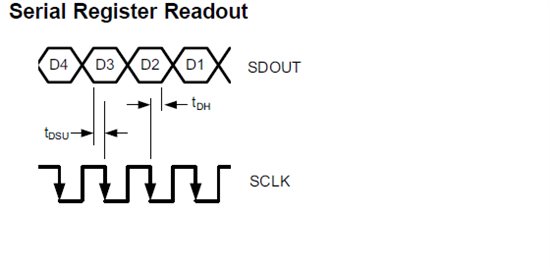

2) What is maximum delay time (set up time) from SCLK to SDOUT at Serial Register Readout?

Best regards,

Masa