Hi,

I am using ADS5282 EVM interfaced with FPGA via HSMC bridge.

My goal is to sample 50 Hz signal with some 1 MHz frequency but minimum clock which can be used with ADS5282 is 10 MHz. I don't mind using even 10 MHz clock but it doesn't sample signals properly below 50 kHz.

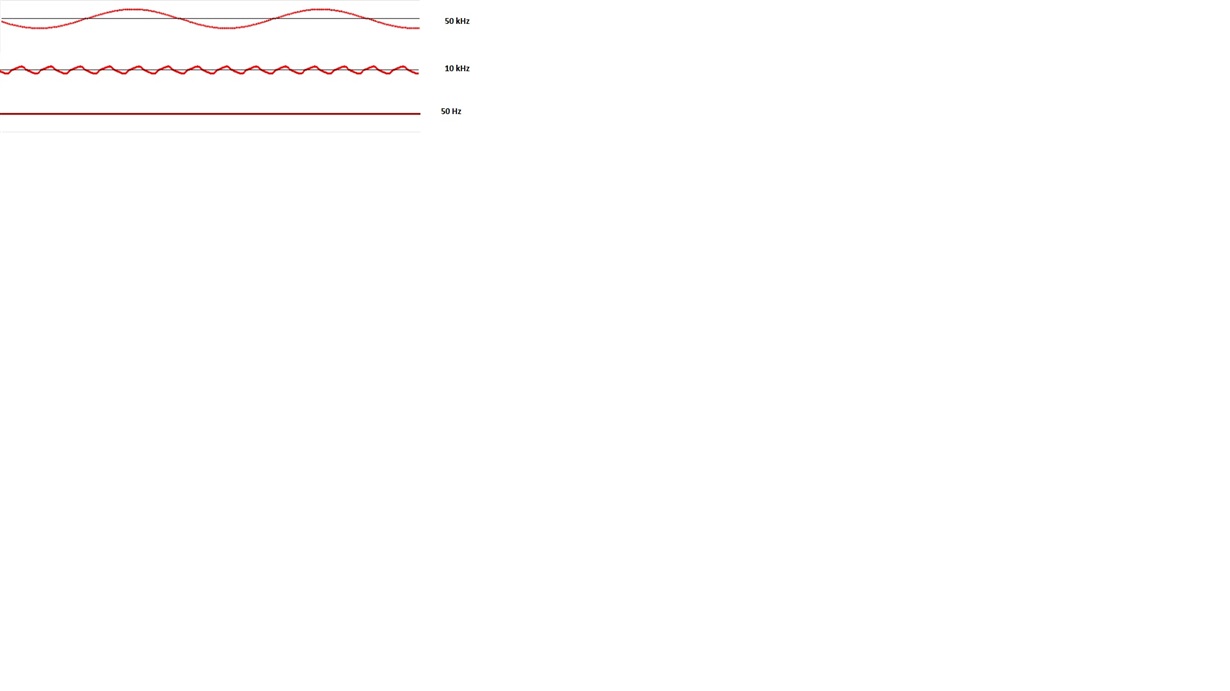

I am attaching snapshots of the signals with 50 kHz, 10 kHz and 50 Hz, respectively sampled with 10 MHz clock.

You can see 50 kHz signal is sampled properly but 10 kHz and 50 Hz signals are not sampled correctly. Although the sampling clock is too much it doesn't show much samples in case of 10 kHz and 50 Hz signals.

Can you tell what is wrong ? How to sample low frequency signals properly ?

Thanks.

BAS