Hi,all

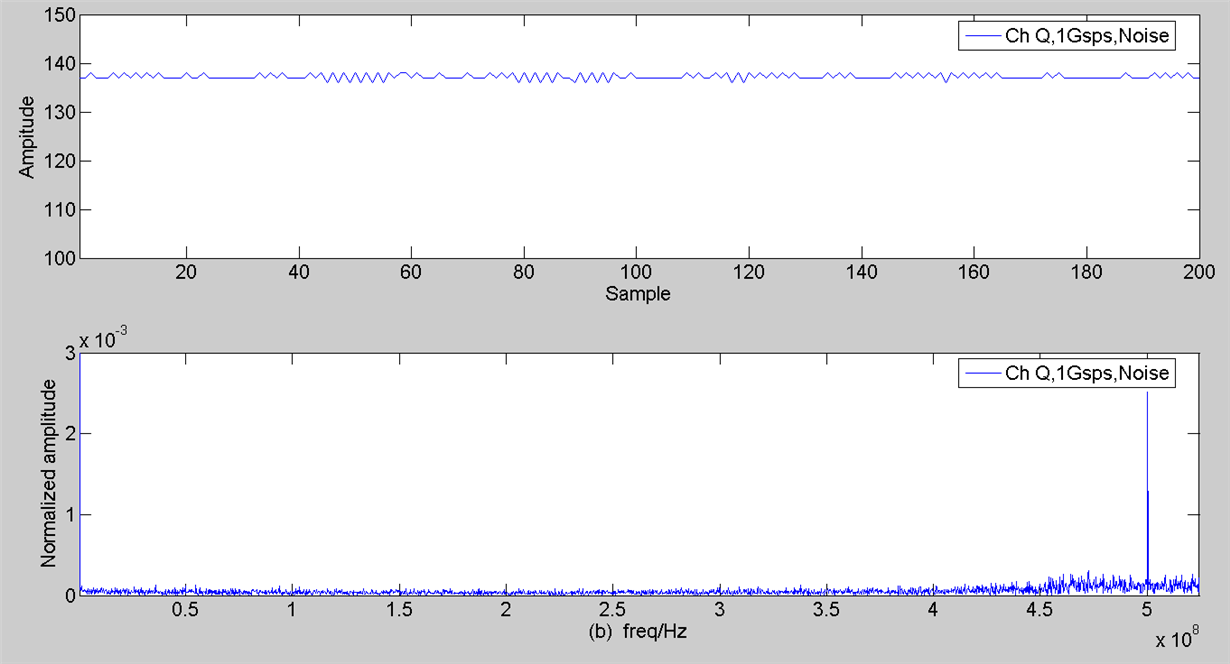

Now i am using ADC08D1020 for data acquisition at 1Gsps.I find that there is a 500MHz noise in signal.I think this may comes from the interference of ADC clock which is supported by LMX2541. The frequency domain digram of the noise is as follows. I hope you can give me some advice.

Best Regards.