Hello,

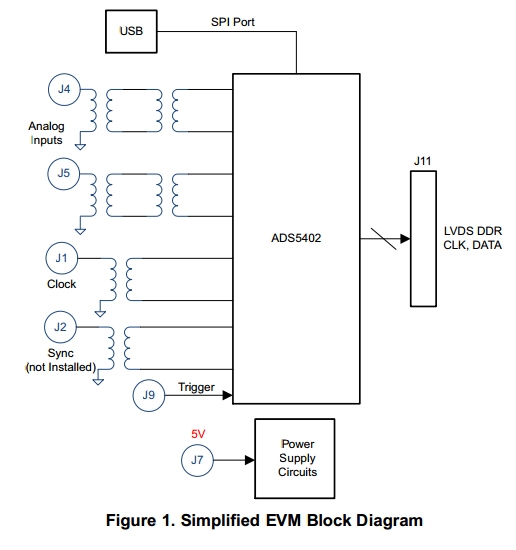

We are using ADS5407EVM. As I learn from the user manual, each analog input is supplied to the EVM through dual transformers, but the clock is through a single transformer. Please see the attached picture.

The user manual says that "A dual transformer input circuit is used for better phase and amplitude balance of the input signal than would typically be produced

by a single transformer input circuit." Our questions is why? We have used a lot of other ADCs and we use one transfomer other than two, and that is OK. Do we have to use dual transfomers with ADS5407's analog input?

Thanks a lot!

Best Regards,

Sam