Hello,

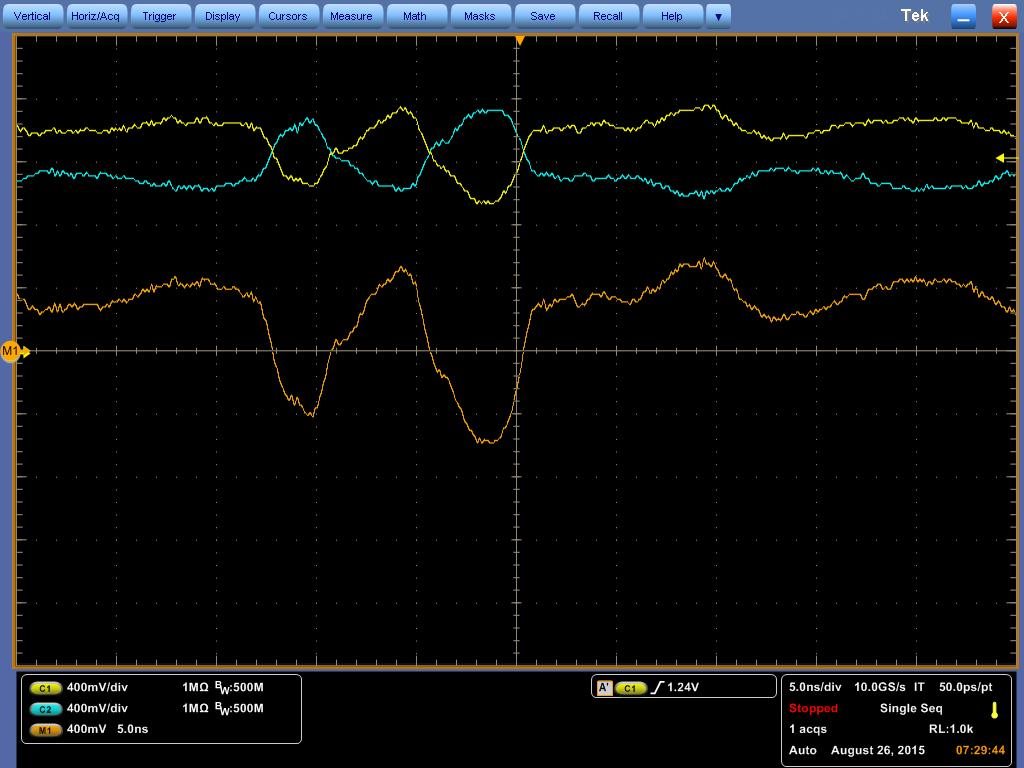

I have been developing some RTL code to capture readings taken from an ADS5463 on ADS5463EVM, I have tracked down a problem when the ADC crosses the "zero" line (2048). I have worked through my RTL for a number of days and have not found in logic problems. I have also checked the hardware and it seems fine the board has not been electrically or thermally stressed in any way. I'm left with the assumption that there is an issue with the ADC.

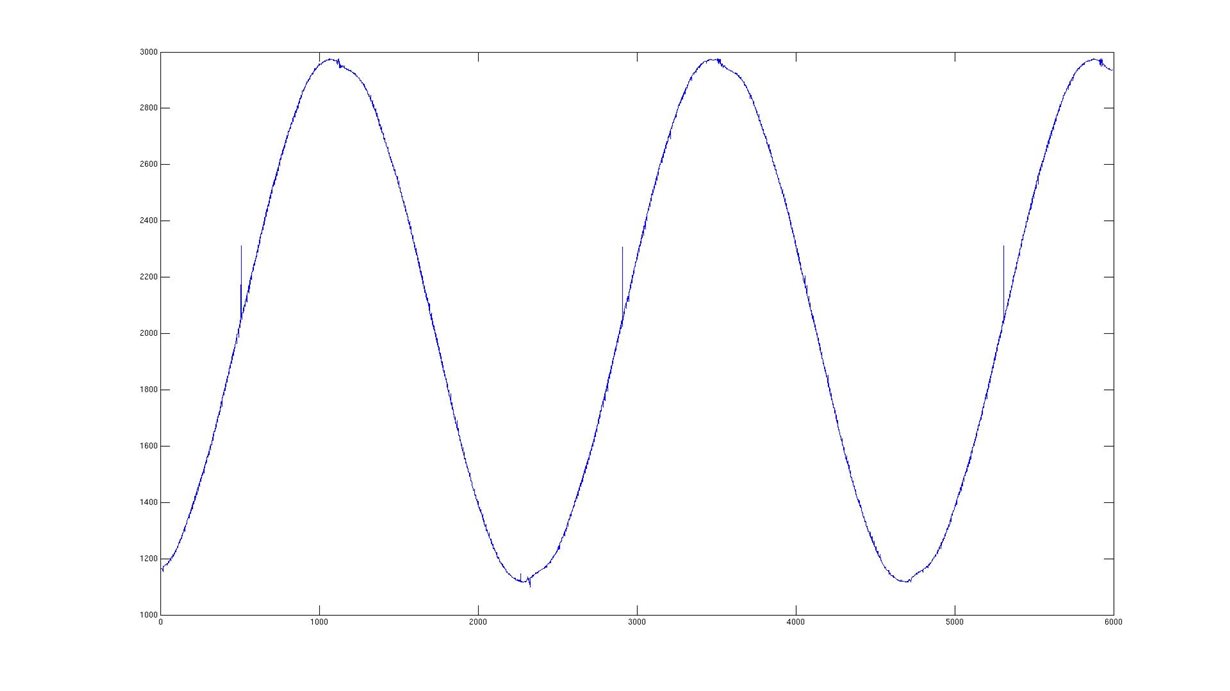

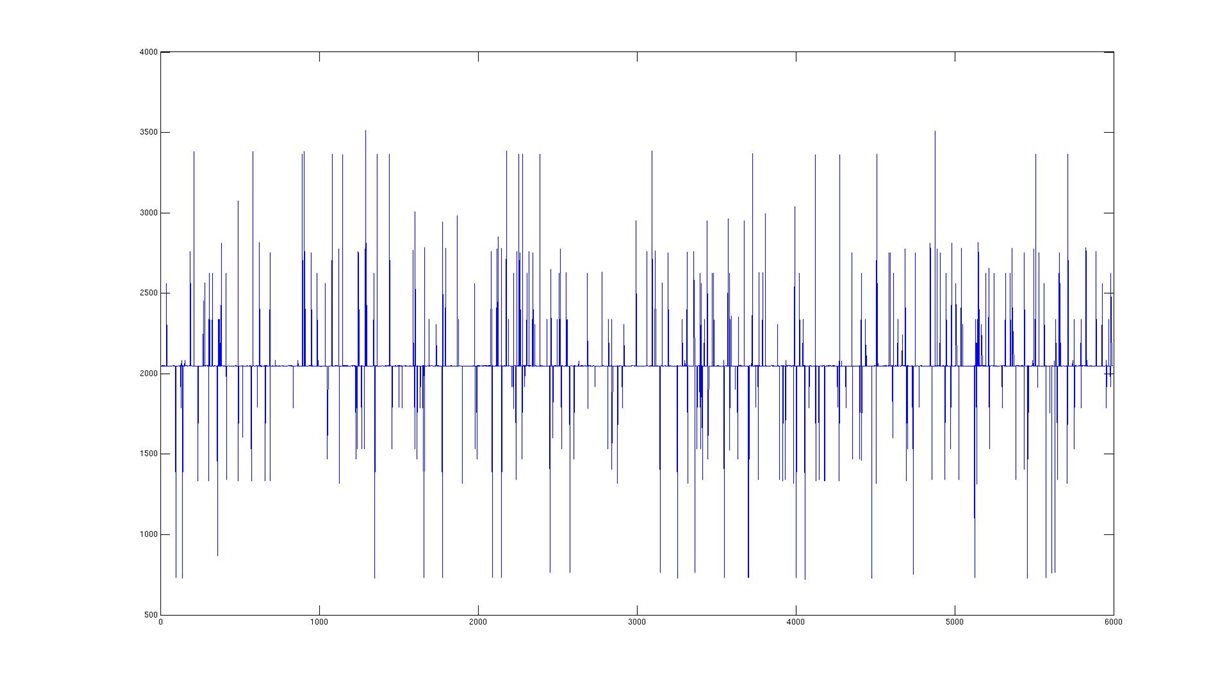

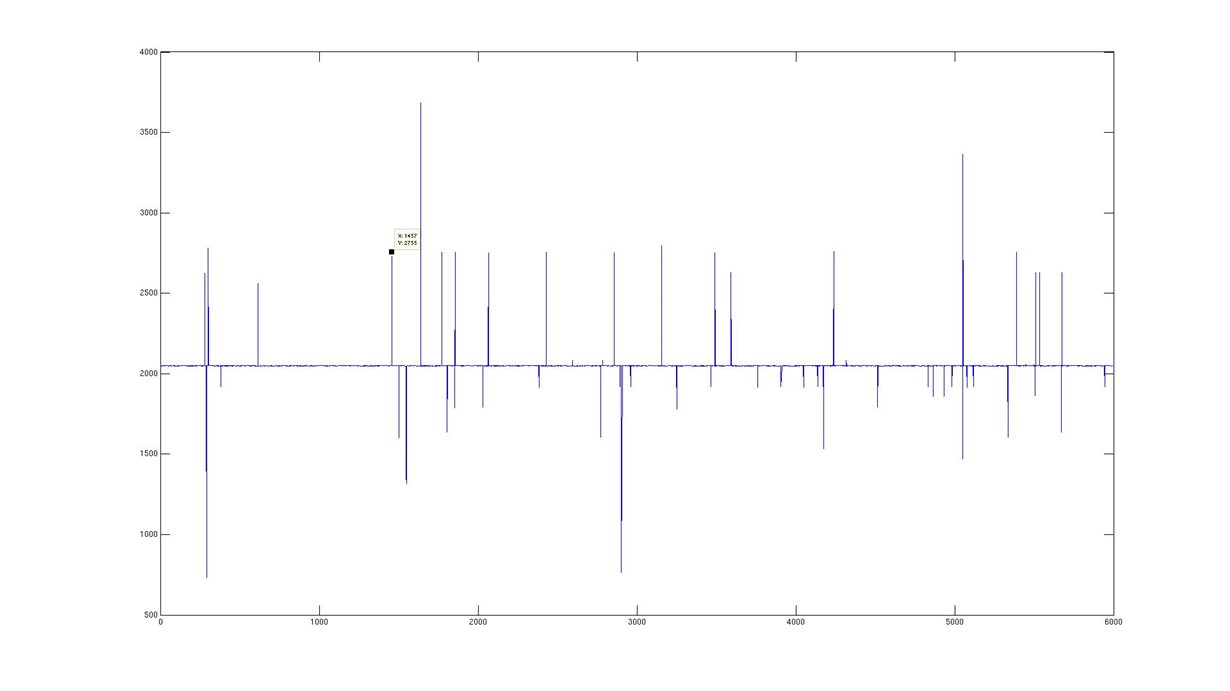

I have attached two graphs showing this error, first graph is from a not so clean sine wave at 166MHz and it is very easy to see the three spikes on the rising edge of the sine wave and the glitch occurs at the 2048 point. The second graph is taken when the input have been tired to ground so I expect it to read a solid 2048 across the board but that is not what is happening. The other case which I don't have a graph of right now is feeding in a steady voltage above zero produces a nice solid line at the appropriate level.

Steps I have taken to try and resolve the problem, I have tried various delay time from the DRY signal to when I latch the data but it does not seem to fix the zero crossing.

Any help that could be offered to point out an error in my thinking or the ADC would be greatly appreciated.