Hello,

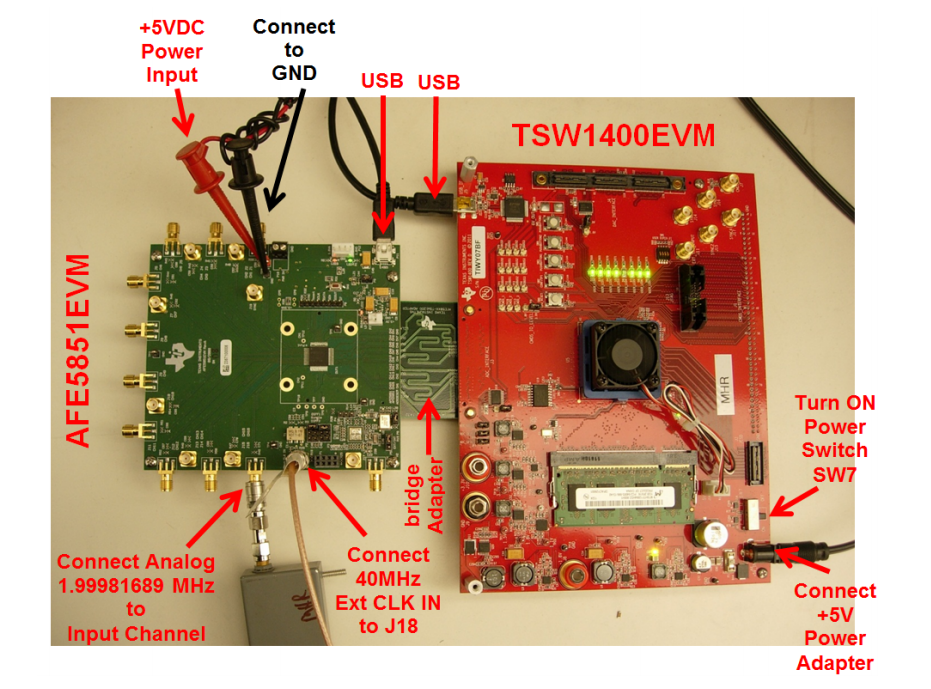

Our team would use TSW1400EVM with AFE5809 to implement our system.

And I have some questions in how to develop our system easier.

As we know, TSW1400EVM has two ways to write code in it.

One is use TI software to write the firmware. The other is change some registers to use the JTAG.

If we use TI software and change our FPGA code to the firmware form, so we can write the code to the board.

But how me know or see the code we writed is good to go ? (How to use TI software to see the result ?)

Because if we use JTAG with Quartus to develop the FPGA code then we would see the I/O, the chip...etc.

And if we use JTAG with Quartus, we would see lots of high and low voltage.

But I afraid that we might not figure out the data is right or not.

So do you have any suggestion to this situation ?

Kind regards,

Jerry