Hello TI,

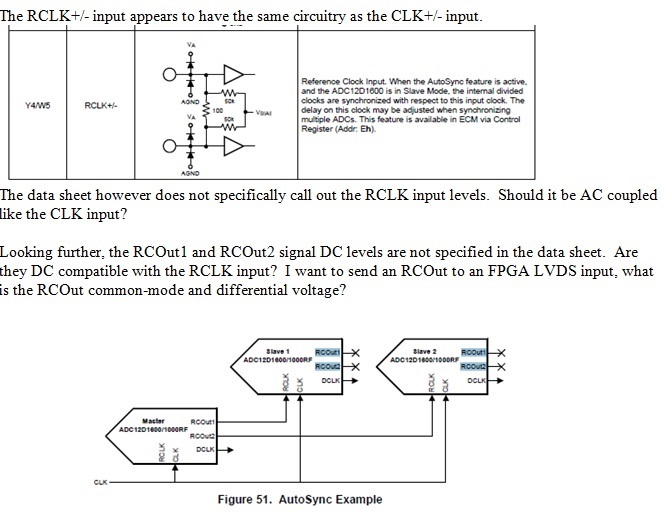

The RCLK+/- input appears to have the same circuitry as the CLK+/- input.

The data sheet however does not specifically call out the RCLK input levels. Should it be AC coupled like the CLK input?

Looking further, the RCOut1 and RCOut2 signal DC levels are not specified in the data sheet. Are they DC compatible with the RCLK input? I want to send an RCOut to an FPGA LVDS input, what is the RCOut common-mode and differential voltage? Refer to figure 51.

Thanks,

Dan