Hello,

We use ADC12D1600RF interfaced with Virtex-6 FPGA in our high-speed EMI measurement system. There have been a number of boards with this ADC that we have used without issues. However, we have disabled on-command ADC calibration due to the uncertainty in the ADC behaviour after calibration. As sometimes it becomes imperative to use calibration to compensate other issues like spurs at fs/2 and aliasing spurs, I need to find a solution for this.

Steps followed to Calibrate the ADC :

1) Prior to every measurement, the ADC is calibrated.

2) Most of the times the calibration is successful, however some other times it is not.

3) I have tried using both available methods to calibrate the ADC - a) Pulling the CAL Pin low and then high (with the Bit 15 of CFG Reg 0 always set to low) or b) Setting the Bit 15 of configuration register 0 low and then high (with the CAL pin always low). In both the cases the low and high times are much higher than what has been specified in the data sheet of the ADC.

What is observed :

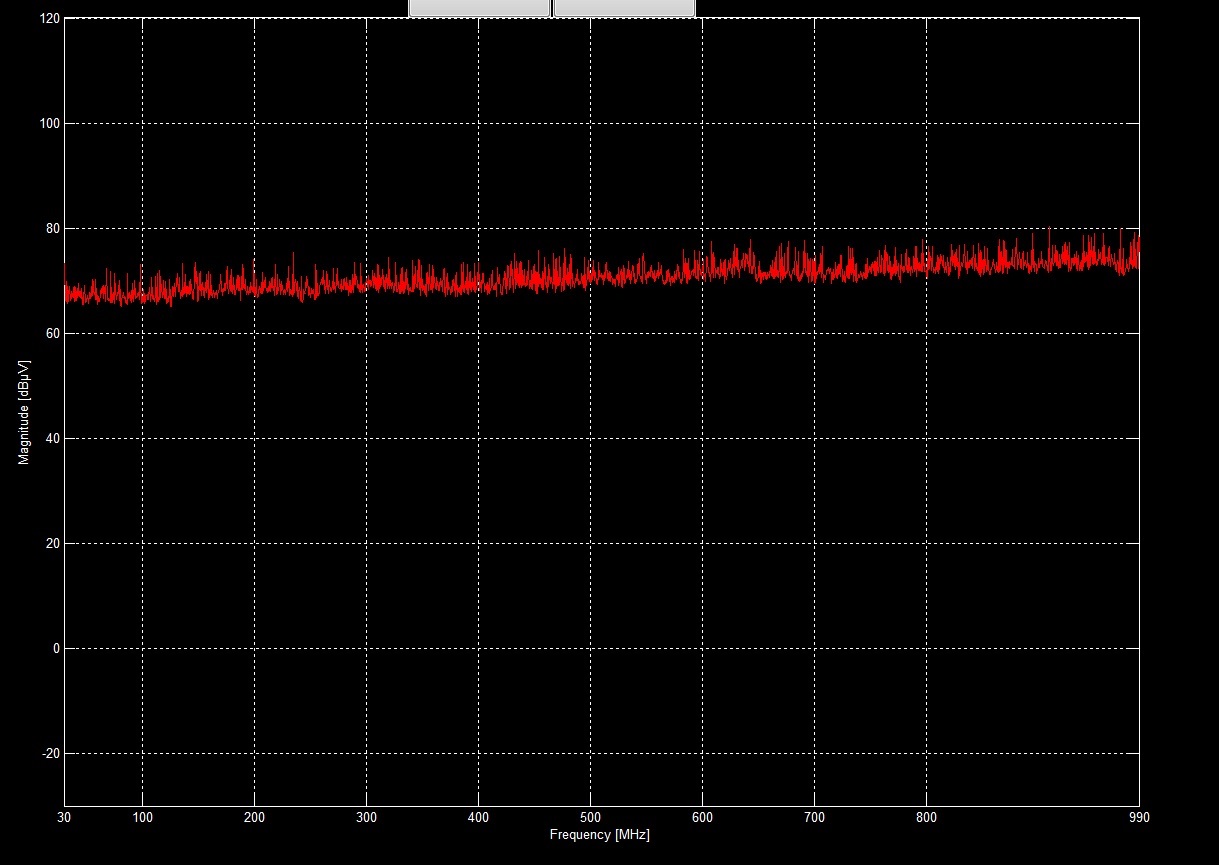

8 out of 10 times the calibration seems to have worked fine. The spectrum of the ADC signal in this case is as shown below (although there is a large aliasing spur at fs/4 + fin):

2 out of 10 times the ADC goes crazy. The below figures illustrate the spectrum of the ADC signal when this happens. You could see the spectrum is completely out of order with a very high noise floor and some other manifestations like bumps, wrong signal levels, non-smooth noise floor etc.

After the ADC goes crazy, on running subsequent measurements (which also does calibration each time), the ADC recovers sometimes but some other times not. For a test system like ours this behaviour is not at all accepted. So, it would be nice if someone could help me out in addressing/debugging this issue. May be there's something wrong that I might be doing.

FYI, the ADC is configured as follows :

1) Sampling frequency is 2.6 GSPS

2) ADC is configured in 1:4 Demux DES Mode with DDR

3) The configuration register values is as given below : (I have also tried only setting Registers 0h and Eh while not modifying/writing into other register locations. But, this did not seem to have any effect)

Looking forward to your help.

Thanks,

Prashanth