Hello!

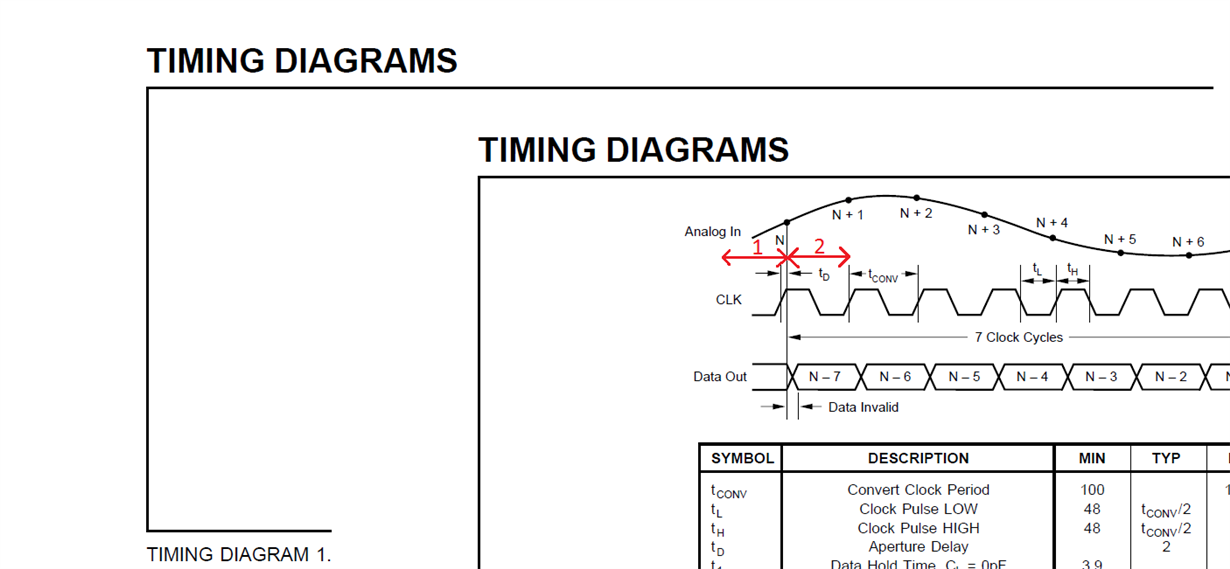

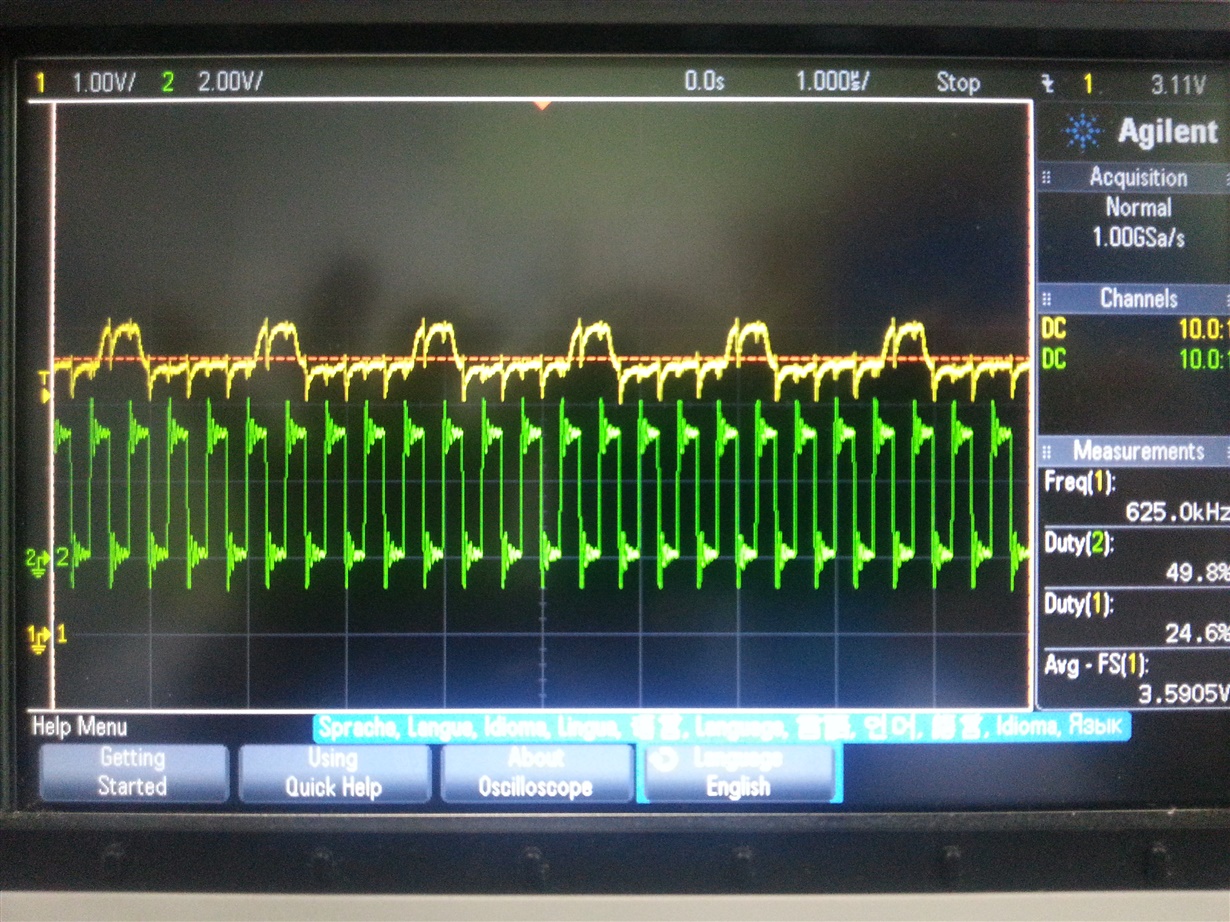

I use ADS850 in our design. I saw timing diagram 1 in ADS850 datasheet. I attached a picture from datasheet. What kind of time region (1 or 2) suggest N sample? How much time needs to acquire input voltage and convert to N sample and where this acquisition time locate on the time diagram?

With best regards, Maxim Galkin.