Hello All:

After established a link between FPGA and DAC37J82, i want to send data to DAC to check whether it's working properly.

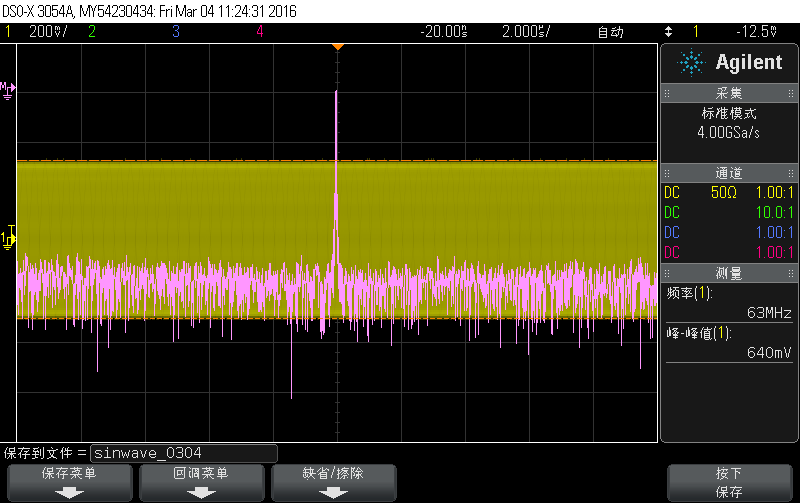

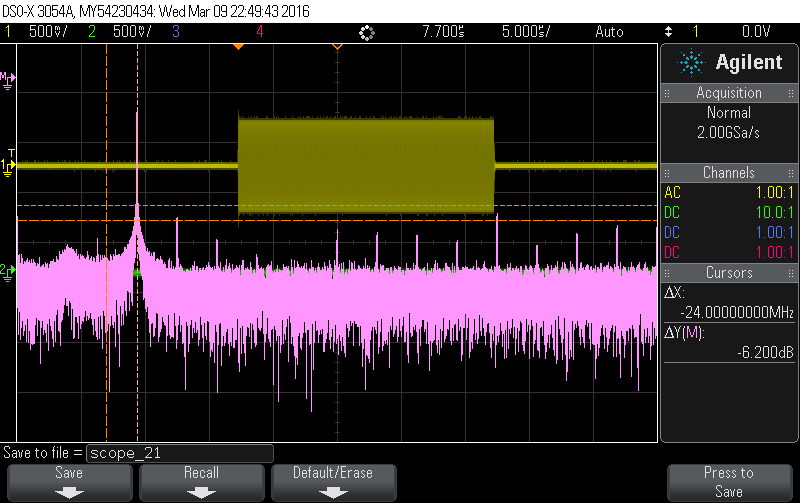

1) when i send constant 0x7ffffff0 (twos complement ), i can get a perfect sin waveform.

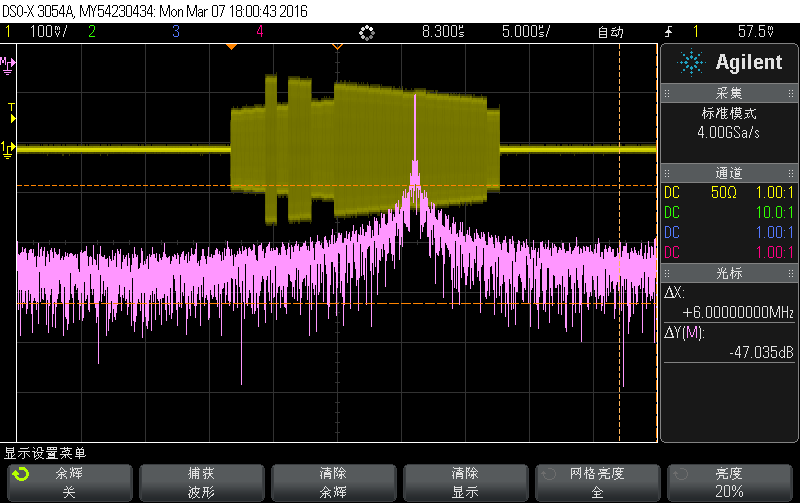

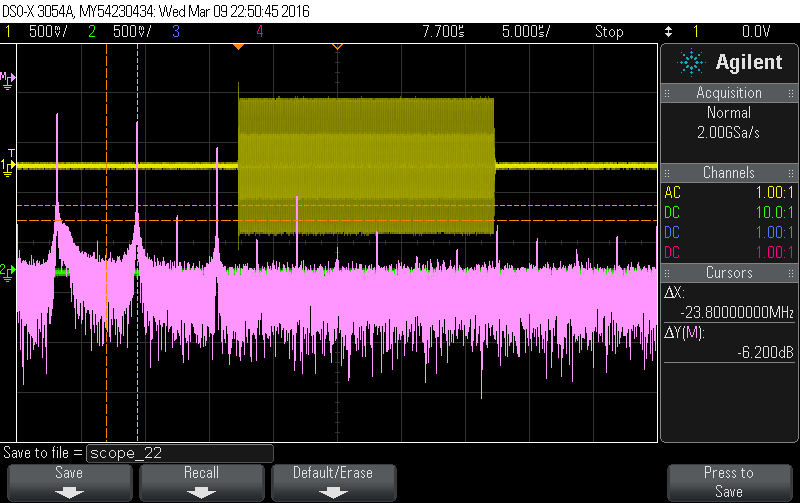

2) The data i send is :0x7ffffff0 - 50000*i . (twos complement ). the image2 attached is what i got from DAC output using oscilloscope.

I think DAC output is out of order. Please help me to figure out what's the problem: DAC configuration errors or DAC is broken

Thank you so much and best regards