Hi,

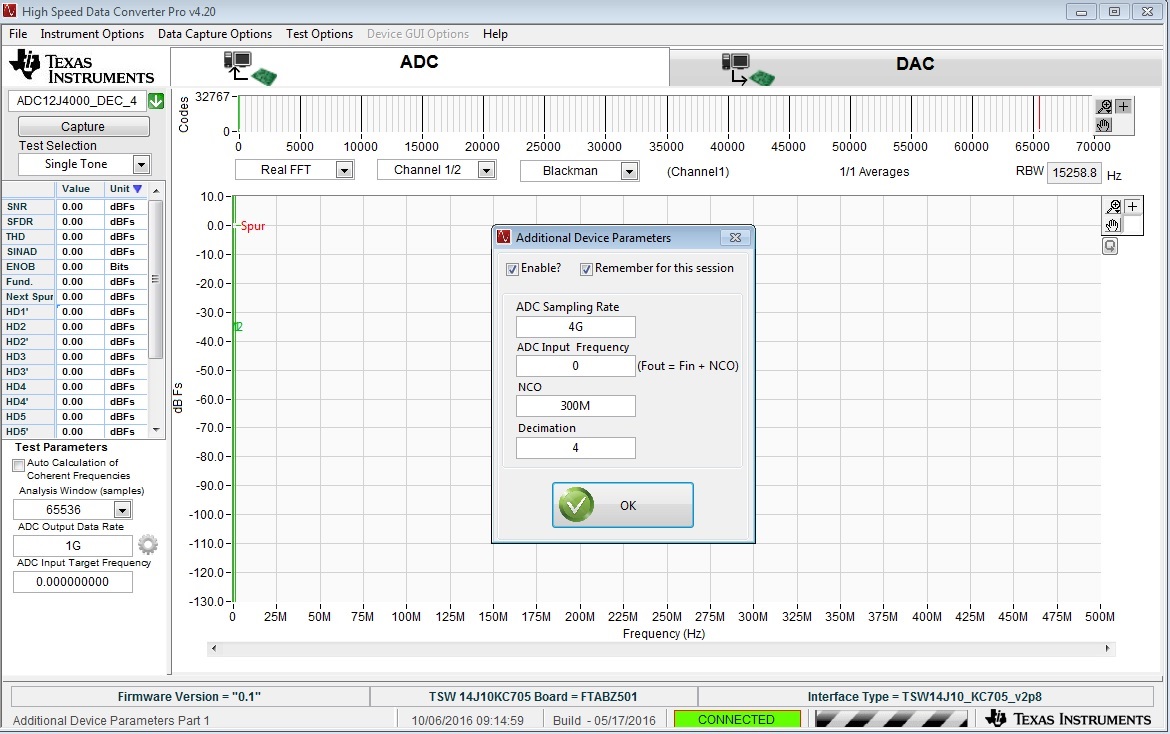

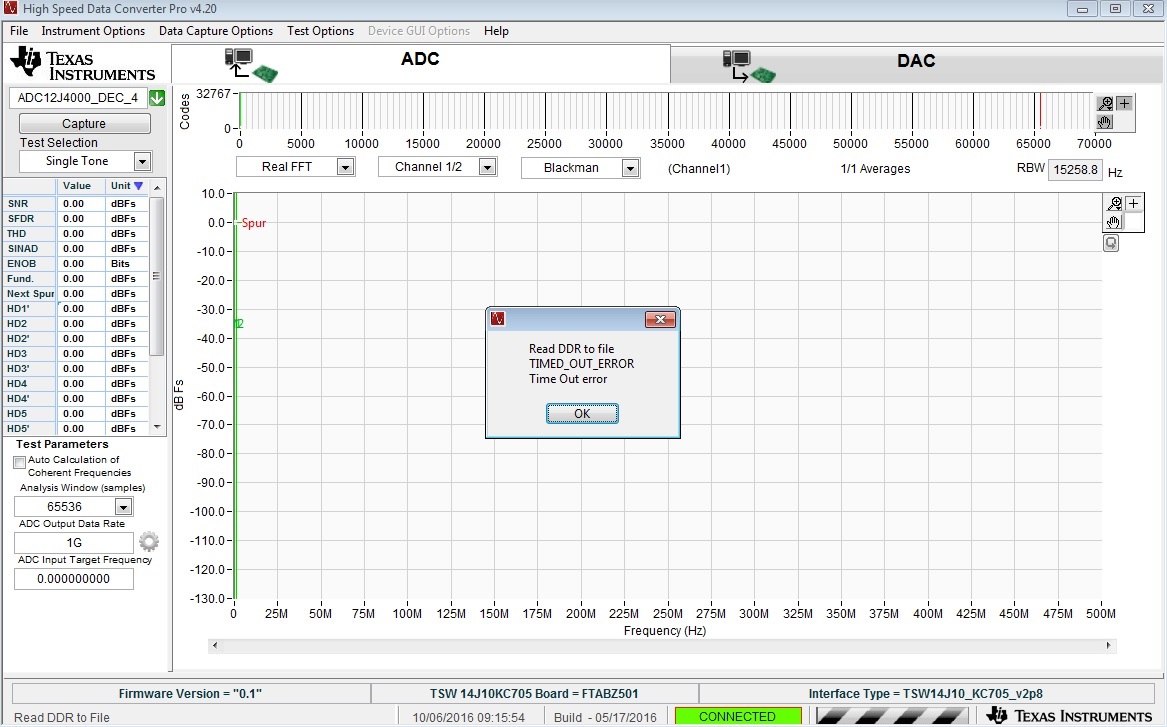

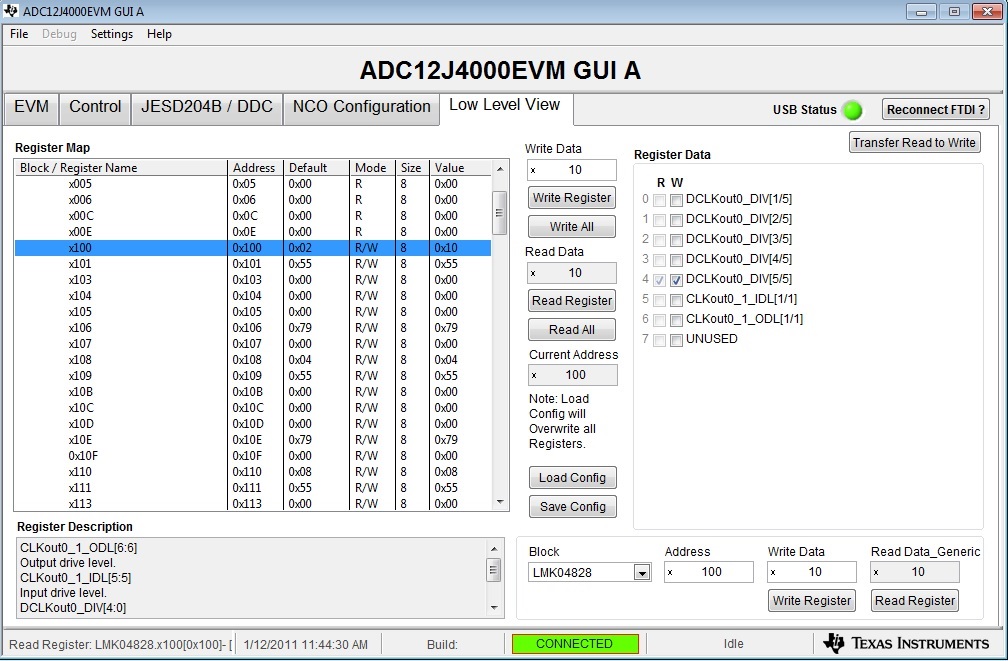

We recently try to capture data from the ADC12J4000EVM to the KC705 platform and display the captured data by means of the HSDC Pro GUI (GUI latest version, firmware version 2.8). We were not able to display the data because each time we click on the Capturing button the error message read DDR TIME_OUT_ERROR. We saw that when the button Capturing is click, the LED 2 goes low (the board is not under reset according to our understanding), the LED4 and LED3 go 0 1 indicating the mode ADC. Leds 5 6 and 7 blink. Everything seems good but any way at the end this error message appears. We also remark that the leds 0 and 1 are high - low. We undestand that this means the jesd_tx_sync goes high and the jesd_rx_sync goes low, Which means that the JESD_RX is either under reset or the synchronization with the JESD on the ADC side was not achieved! We tried to debug with the reference design version 2.8 and we received this. Pleas pay attention to the RX_RESET_REG and the RX_SYNC_STAT_REG.

-------------------------------------

-- RX register Dump --

-------------------------------------

RX_VERSION_REG 0x06010200

RX_RESET_REG 0x00010001

RX_ILA_SUP_REG 0x00000001

...

RX_SYNC_STAT_REG 0x00010000

RX_ERROR_STAT_REG1 0x00000000

-------------------------------------

When we reset the KC705 board and click the Capturing button again, the LED 2 does not even go low. We suppose this is a GUI bug?

We have also a TSW14J56 evaluation board and the data capturing under this board was successful. The problem arises only on the KC705 board.

We have also tested the things on our ZC706 board. Unfortunately the HSDC Pro GUI displays an error message concerning a labview ressource not found!

Please let us know if we must pay attention to some details when capturing data by the KC705. We did pay attention to the fact that the refclk and coreclk should be changed to adapt to the Xilinx design, but that didn't seem to resolve the problem.

Many thanks in advance!

Best Regards,

Tuan