Other Parts Discussed in Thread: LMK04828, DAC39J84

Hi

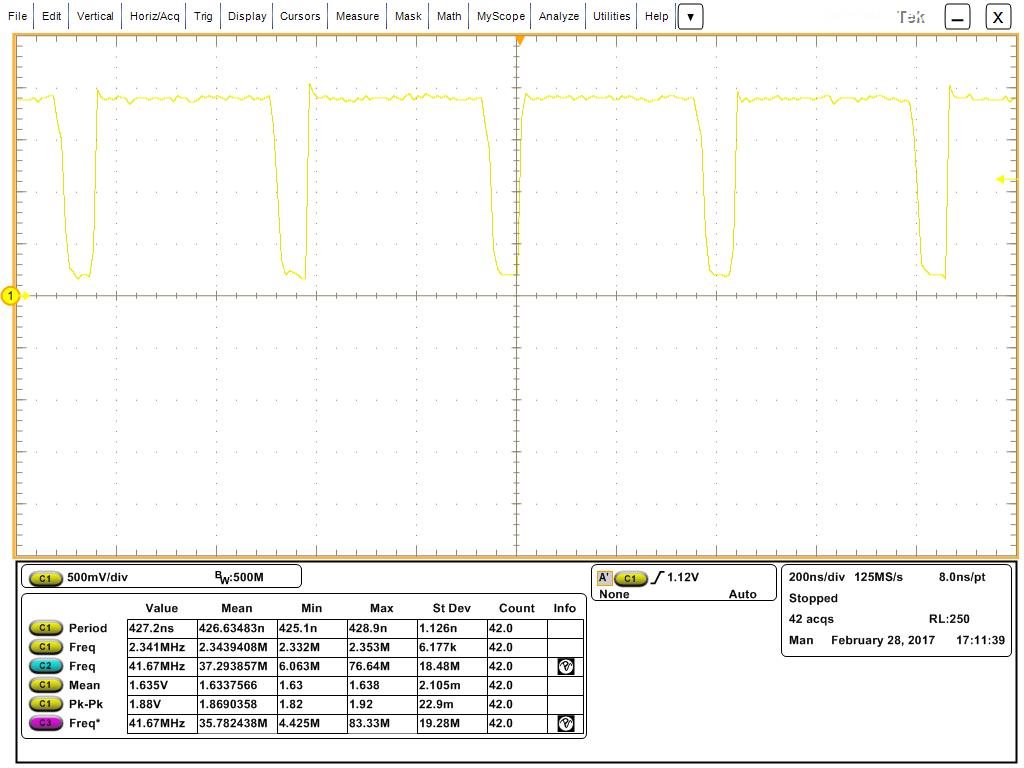

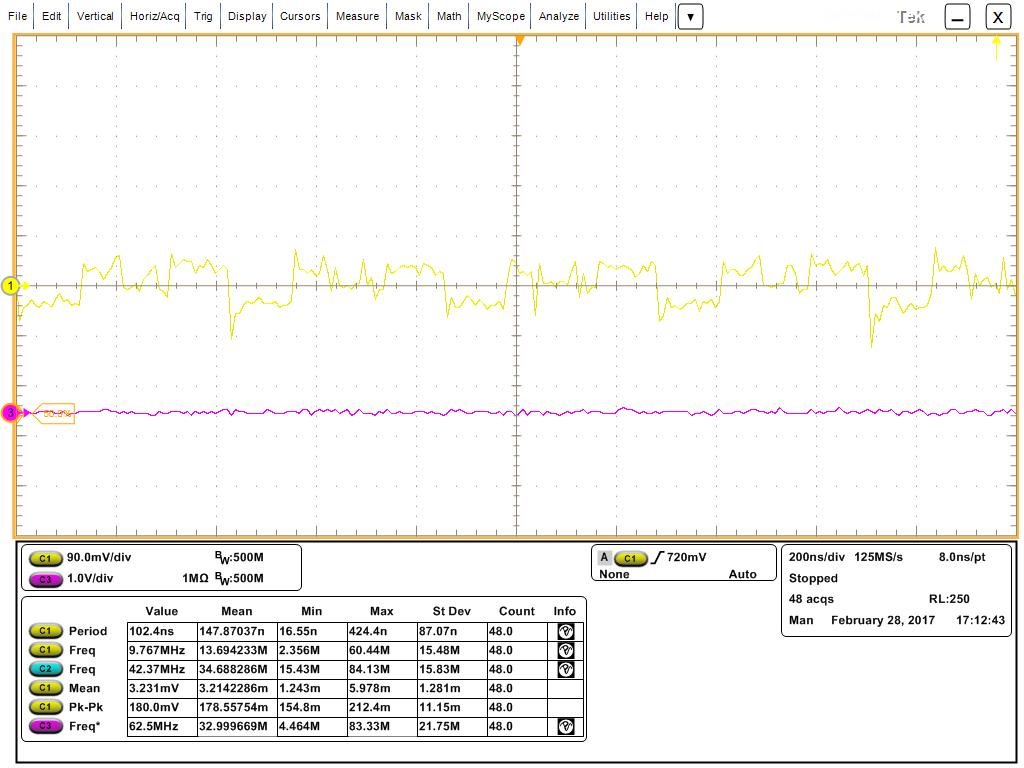

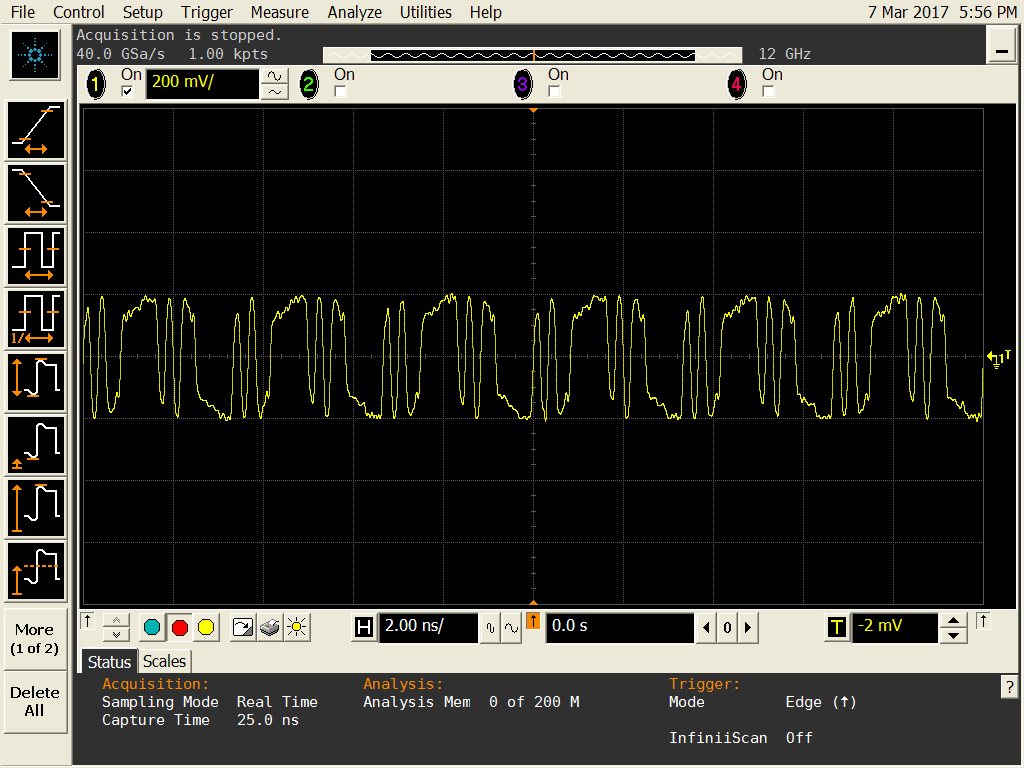

I use Xilinx FPGA and the DAC38J84 to establish the JESD204B developing environment . Now I have some trouble about the SYNC signal. My SYNC can not be toggle. It always stays low. I know CGS is not passed.

The FPGA always transmit the /K28.5/ and I can see the waveform on the oscilloscope . I don't know what's the matter. Does this error come from he registers configuration or the PCB designe? How do I deal with it?