Hi,

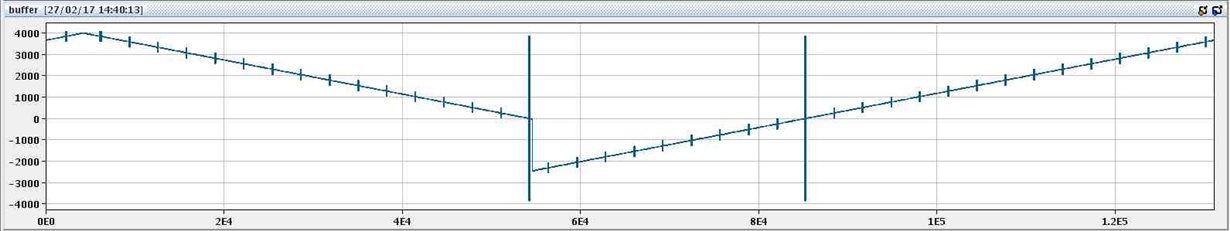

I'm using an ADS6444 linked to a Spartan 6 FPGA and I get huge spikes at the zero crossing.

1st thought, it was related to deserialization, data/clock alignment issue, but arbitrary frames (toggle, sync, custom, etc.) seems to work fine.

Changing the encoding from 2's complement to raw binary doesn't change much either.

Moving to possible analog issue, both the ADC power supply and (internal) reference voltages seem clean.

My signals measured directly on ADC inputs seem also clean.

Any suggestions? Still if it is a digital or analog problem...

Thanks.

Best regards,

Jerome