Hi,

I am running a test using an SMA100A signal generator in pulse modulation mode. I have a minicircuits splitter which I splits the sig gens output into channel A and B of an ADC32RF45EVM.

I set up the ADC and LMK Clock Chip using the old GUI (ADC32RFxxEVM_revD_GUI) with the following parameters

- Fs = 2949.12MSps

- DDC set to 4X decimation IQ

- DDC frequency is set to 0

Signal Generator is set to:

- 20MHz Pulse modulation 0dBm

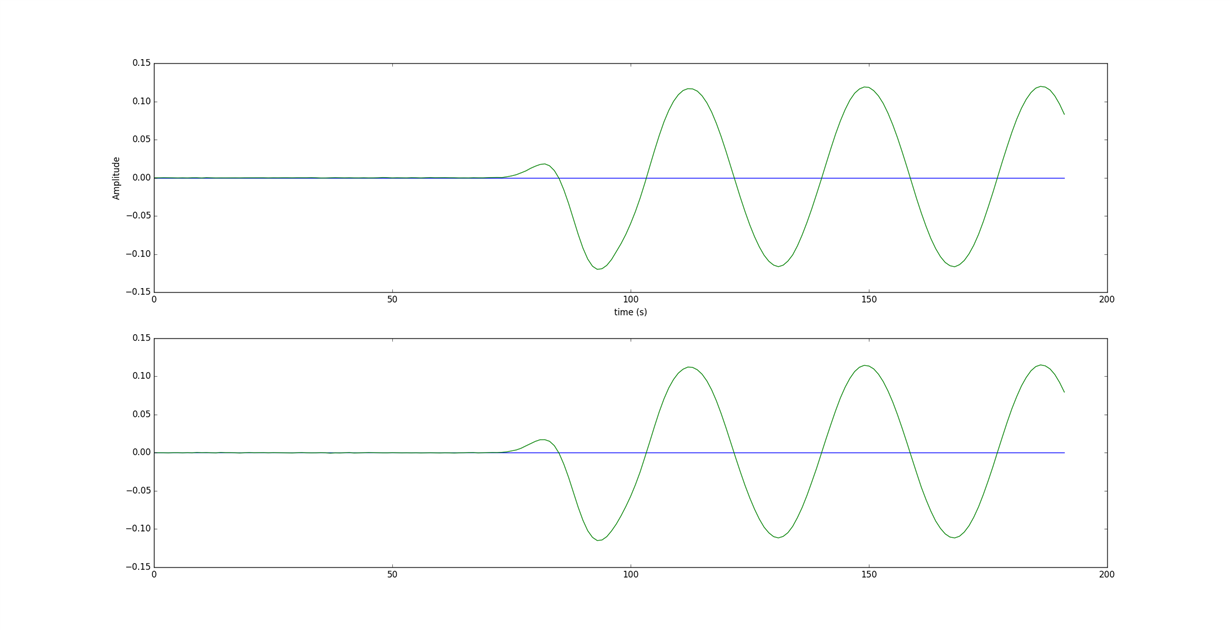

I then capture and plot a set of samples. This is shown below.

The first plot is IQ for first ADC Channel and the second is IQ for the second ADC Channel. [Disclaimer: The time scale is in in samples not seconds. I forgot to change the title]

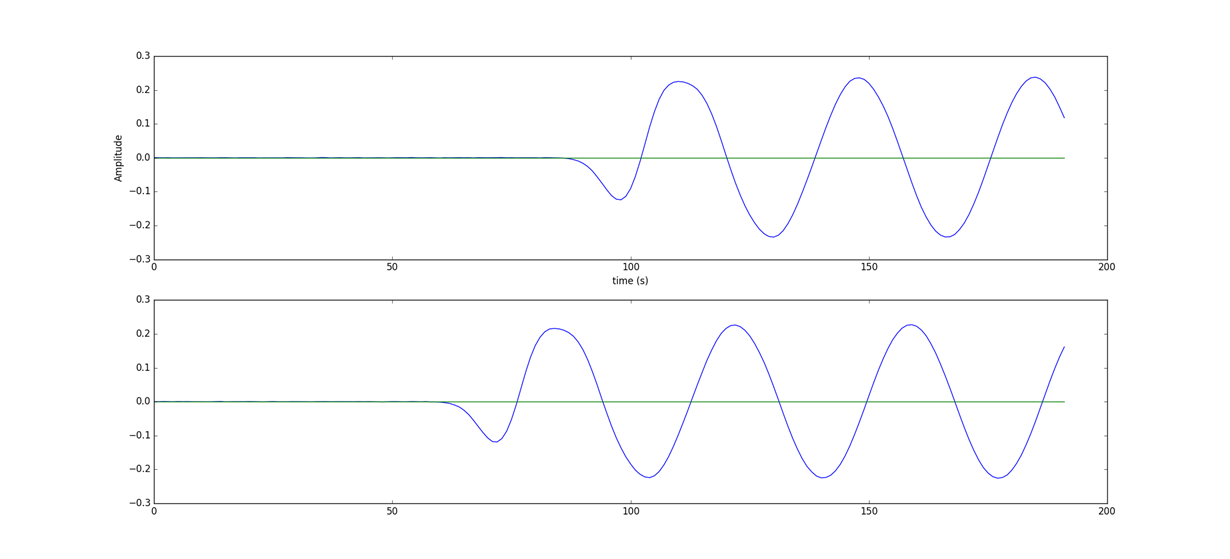

I repeat the exact same test using the new GUI (ADC32RFxx EVM GUI) to set up the ADC and Clock.

In this case the plot (as shown below) contains a time offset between Channel A and B.

I would appreciate any feedback or ideas as to why this may occur.

Kind regards,

Matthew Bridges