Hello,

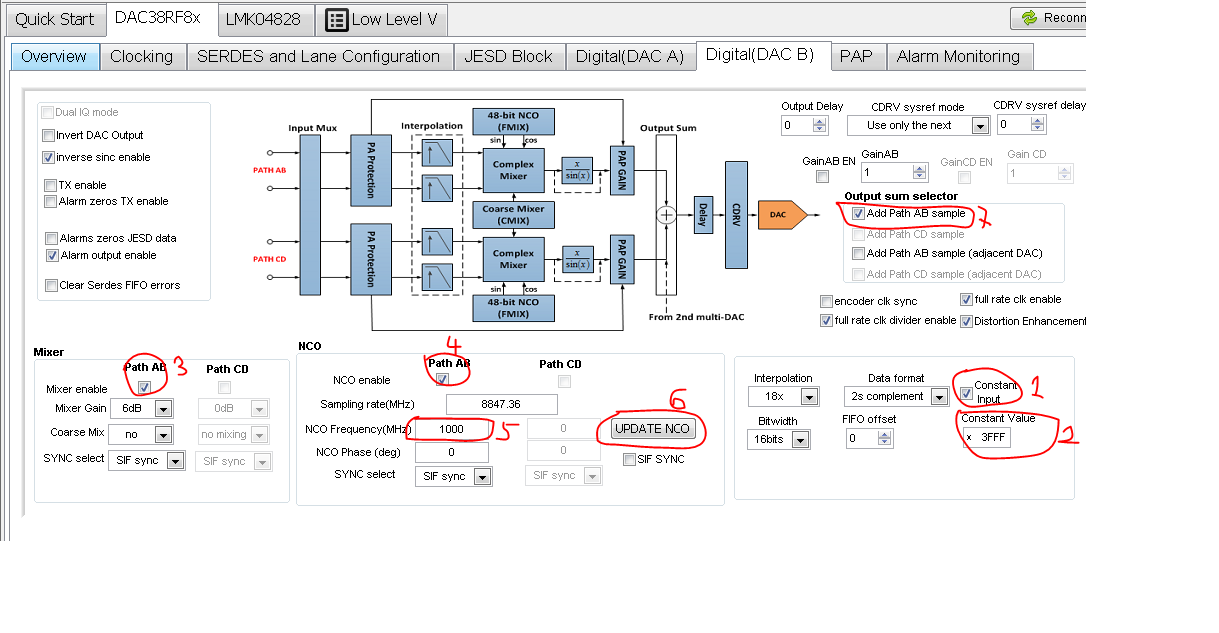

I tried numerous of times to configure the DAC38RF82EVM with the GUI (CMODE3). I use the manual ('SLAU671A' section 2.1.4 DAC38RF8xEVM Configuration With On-Chip PLL(CMODE3)), but unfortunately there is no RF output signal on the spectrum analyzer visible. The boards are all connected onto a 5V power supply and USB (as described in the User's Guide).

Both boards are recognized by the GUI (green light is on), but when I try to send the described (384M data rate, 100k) single tone sequence of the TSW14J56 board (HSDC GUI) the following window appears:

Additionaly on the TSW14J56 Board the LED D8 (Mem Fail~) is lighted as well as LED D2 (Tx CLK).

TSW14J56 (HSDC GUI):

used firmware: DAC38RF8x_LMF_841

DAC38RF82EVM (Hardware configuration):

- JP2 (Shunt pin 1-2: Enable DAC output)

- JP10 (Shunt pin open: Enable on-chip PLL clock mode)

- SMA J4 (Ref Freq. 384M, 6dBm)

Since I use User's Guide configuration, what can be the source of the setup problem? Moreover, is it possible to get any additional information/documentation regarding the DAC38RF8x EVM GUI since there are a lot configuration options?

Kind Regards,

Ivan