Other Parts Discussed in Thread: LMK04828

I'm using the ADS54J54 in conjunction with the LMK0428 clock jitter cleaner and am observing strange behavior from the ADC. The LMK0428 is providing 500 MHz clocks, as well as the SYSREF input to the ADC. I am using a pulse/one shot method for SYSREF, which was recommended by the datasheet.

Here's my steps and results:

I program the ADS54J54 using the following steps from the datasheet:

7.3.12 JESD204B Interface Initialization Sequence

After power-up, the internal JESD204B digital block must be initialized with the following sequence of steps:

1. Set JESD RESET AB/CD and JESD INIT AB/CD to 0 (address 0x0D, value 0x0000)

2. Set JESD INIT AB/CD to 1 (0x0D, 0x0202)

3. Set JESD RESET AB/CD to 1 (0x0D, 0x0303)

4. Configure all other JESD register and clock settings. If those settings change later on, this initialization

sequence must be repeated.

5. Set JESD RESET AB/CD to 0 (0x0D, 0x0202)

6. Set JESD RESET AB/CD to 1 (0x0D, 0x0303)

7. Wait for two SYSREF pulses

8. Set JESD INIT AB/CD to 0 (0x0D, 0x0101)

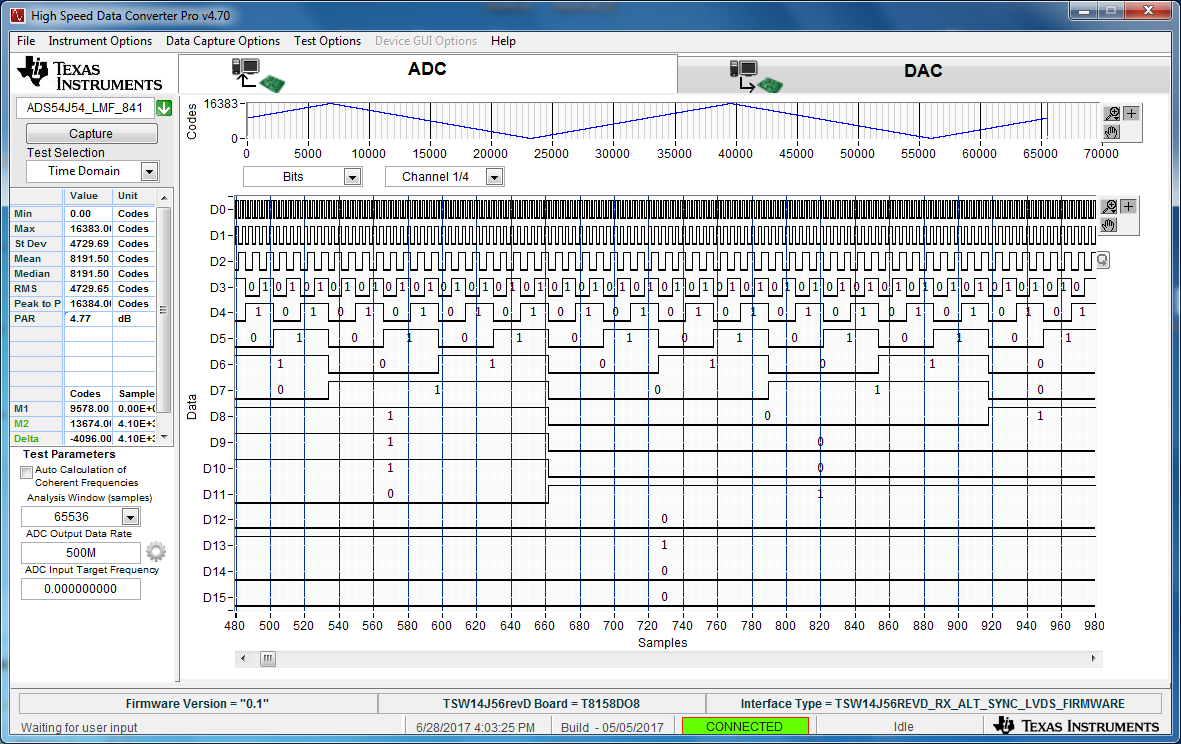

After step 8, the device immediately starts sending K-characters. This is not expected. According to the data sheet, I shouldn't receive K-characters until SYSREF is asserted followed by a SYNC. See the figure below. If I assert SYSREF, then the k-characters stop momentarily, and other characters are transmitted, but they aren't consistent with the ILA process. After a few dozen random characters are received, the received data returns to being k-characters indefinitely.

Oddly, SYNC, doesn't seem to have any affect on the ADCs behavior.

Thanks in advance for your help.