We've got the ADC31JB68 connected to a Xilinx Artix-7 FPGA, and are using the giga-bit transceiver GTP IP to interface to it.

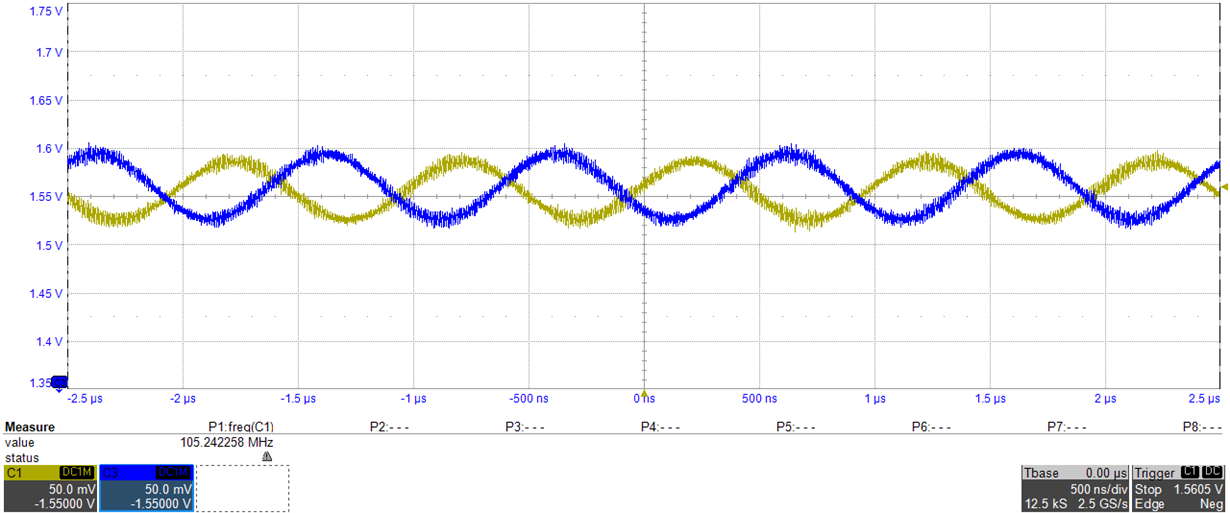

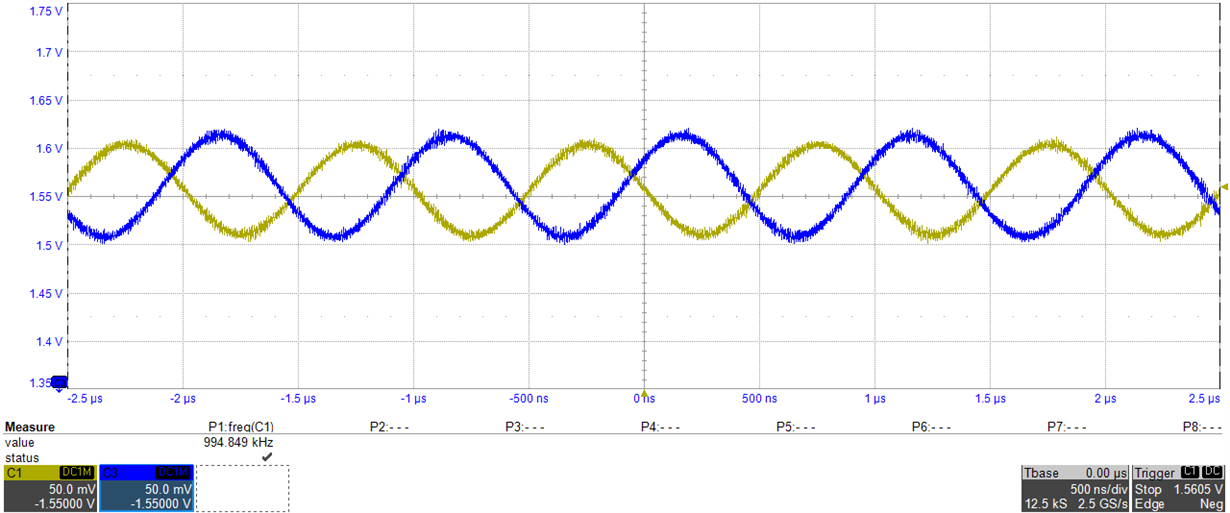

The problem is when sync is driven low after power-up. K28.5 data is expected on both lanes (xBC seen on the parallel data output of the Xilinx IP). Sometimes both lanes send this data and when sync is driven high, correct captured data can be seen. The interface will always behave correctly from here. However on other occasions neither or only one of the lanes transmits K28.5, and no combination of resets or re-syncs seem to change this. Reloading the FPGA image will change the lanes that output correct K28.5 data.

It would appear that there is some kind of power-up or data alignment issue.