Other Parts Discussed in Thread: DAC3154

Hello,

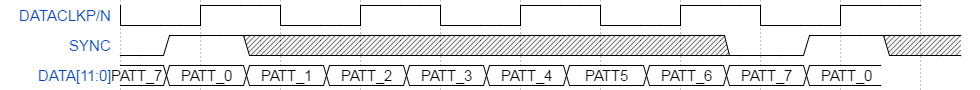

I am trying to use the IO test feature of the DAC3164 to verify that the digital interface with an FPGA is functioning properly. I read this thread, which provides some information about using the IO test feature, but I need some additional information.

How are the iotest_pattern0-7 fields in the SIF registers are used for the IO test when the digital interface is used in dual channel DDR mode? Are all the patterns in iotest_pattern0-7 compared to both channel A and channel B? Or are some of the patterns compared to only channel A and some of the patterns compared to only channel B?

Thanks,

Royce