Part Number: TSW14J10EVM

Hi Support,

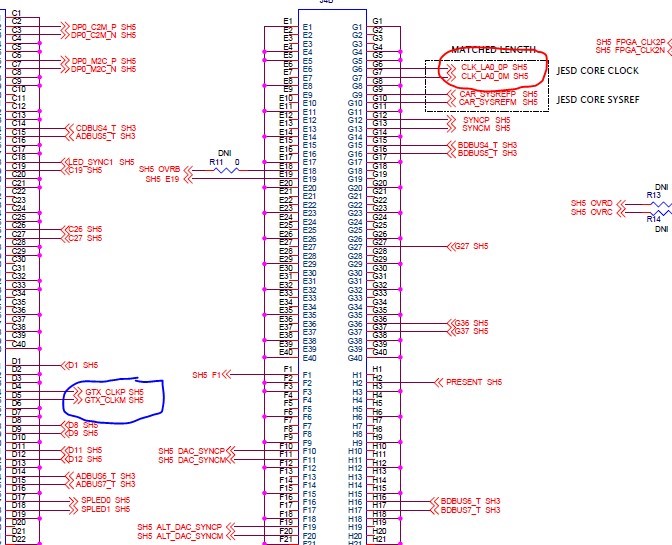

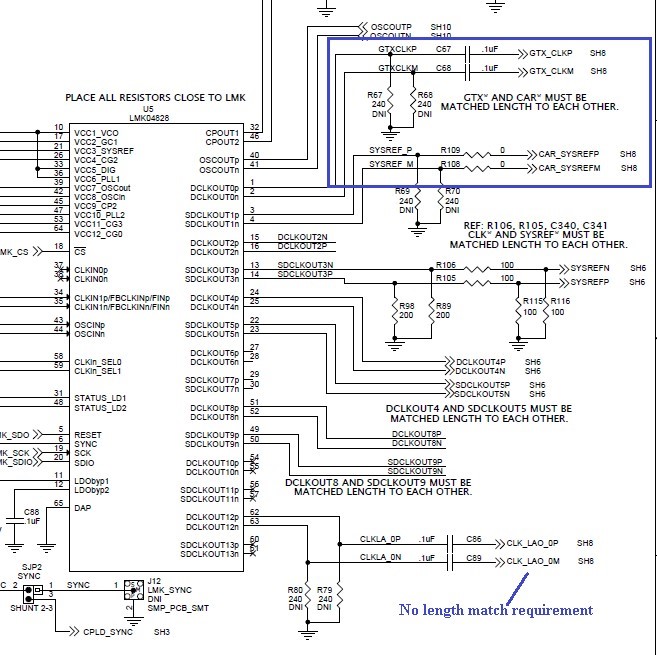

With reference to TSW14J10 schematic Page 4 attached...

Does SYSREF has to be length-matched with GTX_CLKP/M or CLK_LA0_0P?

Note that on the FPGA, GTX_CLKP/M goes to the GTH high-speed transceivers to which the high-speed serial lanes are also connected.

CLK_LA0_0P/M are connected to a normal MRCC bank on the FPGA.

Thanks.