Hi,

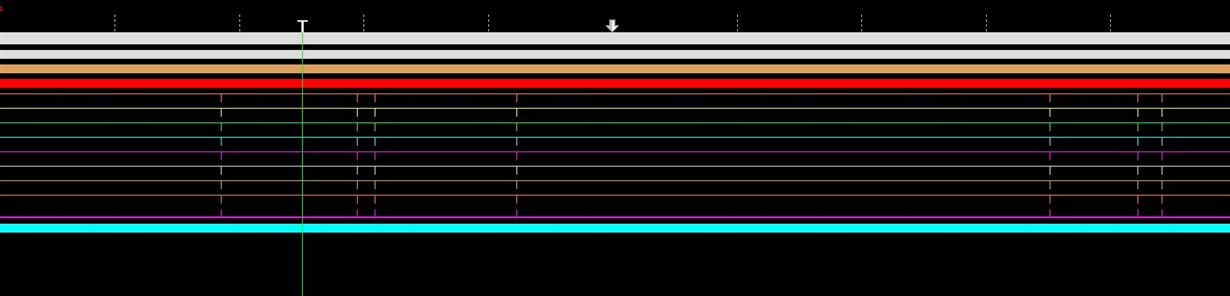

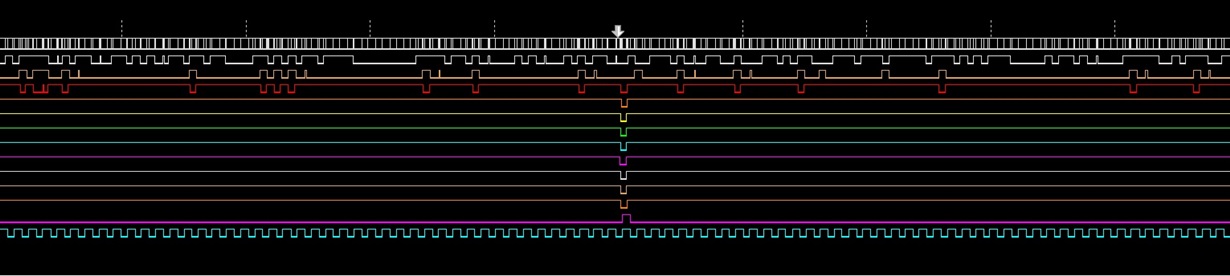

Now I am working with ADS5463EVM and I connected LVDS output to Xilinx zynq soc chip. I converted all LVDS output to single end with have enabled terminal resistors inside the zynq device. I am reading ADC output every DRY in positive edge without and delay But output signal has a lot of glitches.

1) what is the reason of these glitches? is it probably relate the reading time? what do you suggest?

2) I know the ADC outputs are changing every edge of DRY, what is the best solution to read the data inside the FPGA on both edge?

Thank you,

Amir

.