I am using the DAC37J82 on our design.

The DAC37J82 is being used with the following Serdes configuration:

LMFS 2221

K=16

Sysref : 9.6Mhz

Fs : 614.4Mhz

interpolation : 4

Lane Rate : 3072Mbps

153.6Mhz

External Clock mode.

Complex.

We do not have EVM.

We are use GUI simulation.

I revised the board.

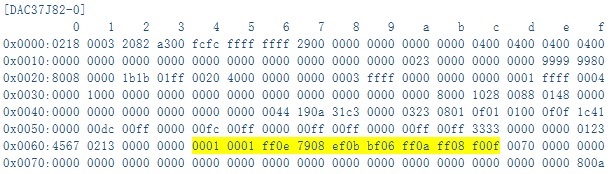

I set a DAC37J82 register for E2E's reply.

The E2E file is "DAC37J82 Fs 614.4 K 16.cfg".

Our problem is as follows.

JESD204B link not connecting.

JESD204B PLL does not lock.

What is the way to check JESD204B?(Register check?)

Thank you