Hi,

I would like to use an ADS8556 in software mode and serial interface (with a SPI).

I am using ADS8556EVM. So here is the jumpers configuration:

- JP1,JP2,JP5,JP6,JP7,JP8 : 1.2

- JP3 : 7.8

- JP4, JP10, JP11 : 2.3

- JP9 : 1.2, 4.5, 7.8

- JP12 : close

The switch SW1 configuration is :

- word

- 4x

- SFT

- SER

- REFBUF ENA : 1

- Daisy chain ena : 0

- SERA enable : 1

- SERB enable : 0

- SERC enable : 0

- REFen : 1

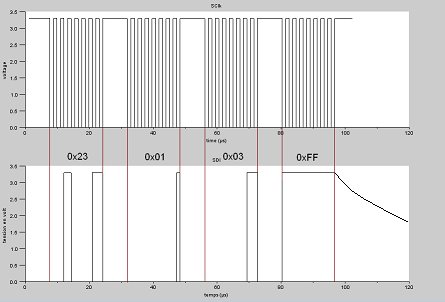

The value of the control register is : 0xE30103FF (sent to SDI pin)

Even if I am working in serial mode, I have to use DC_TOUT and DC_INTa pins on the parallel control port (for CONVST_A and BUSY respectively). Am I wrong ?

Unfortunately, I have no signal on SDO_A ouput ( I only use this pin to read the converted data of all analog inputs).

Thanks in advance for any idea to solve my problem.

Regards