Hi All,

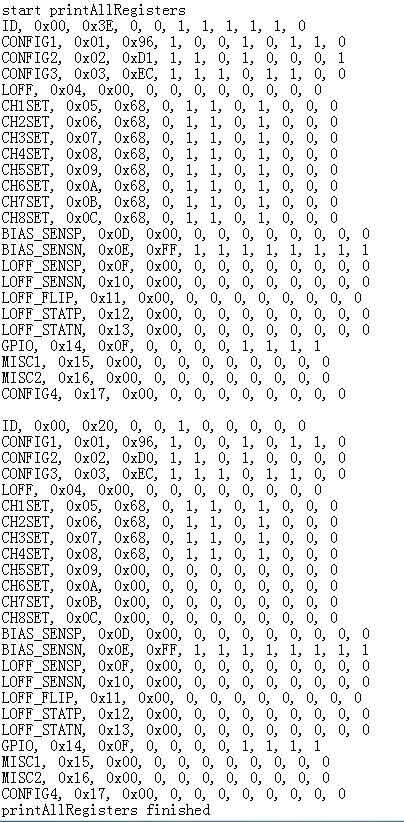

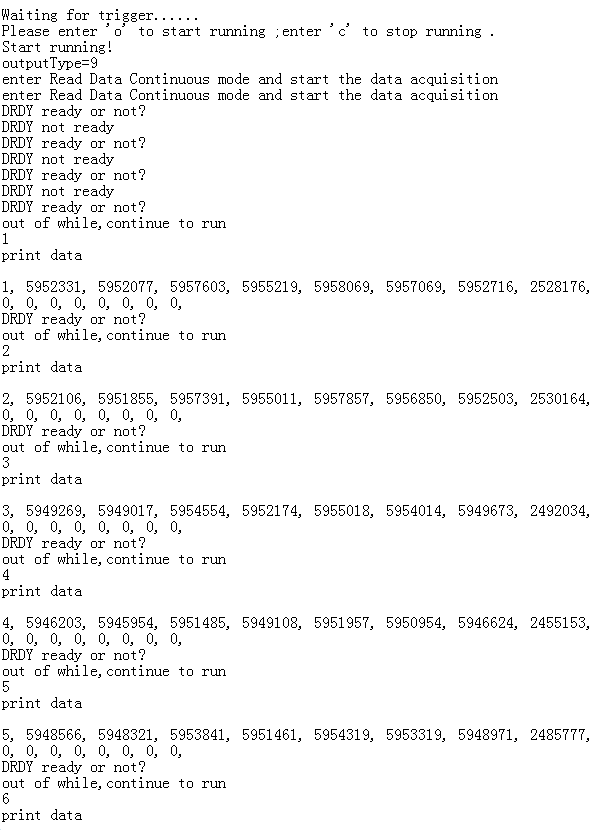

This is the second time I've run across this, so I'm hoping that someone else has seen it as well. I am configuring an ADS1299 by writing data to the registers. As a verification, I read the data back. Invariably, CH5SET..CH8SET all read back as 0x61, although I'm trying to write them as 0x00.

Any ideas as to what would cause this?

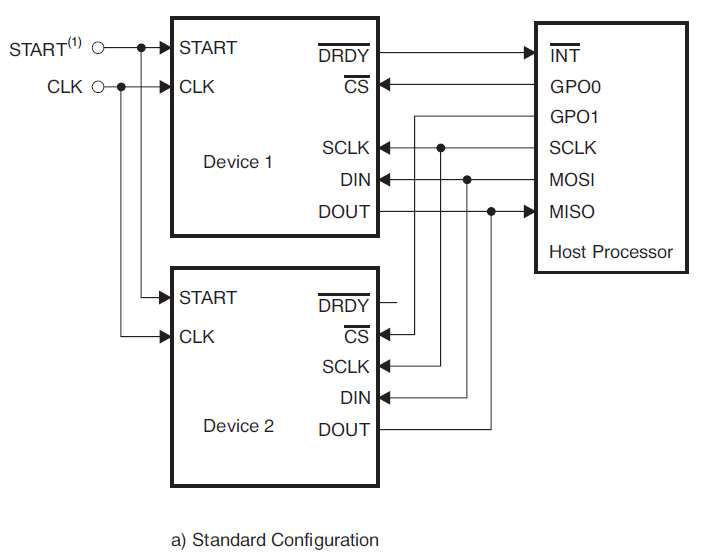

I'm reasonably certain it is not an issue with the code that is updating the registers -- I can modify and read back CH1SET..CH4SET, and there is an ADS1298 attached to my system that I can modify without issue (and I've verified it on both a Logic Analyzer and a scope)

I'm not sure if it is important, but the ID register is 0x20, which is odd, since I think it should be 0x1e.

Any help would be appreciated,

Brian LeLacheur

Natus