Hi,

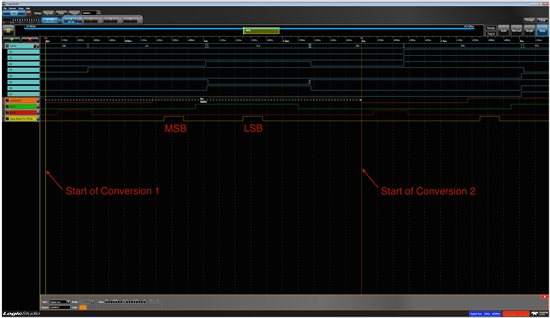

In the ADS8422 ADC, can I tie the nRD pin to ground and just use the nCONVST to do the actual clocking?

Does the nRD pin have to be clocked as well to shift out the data?

I'm trying to minimize the interface pin count.

If that won't work, can I tie the BUSY pin to nRD so that it essentially asks for data automatically when it's ready?

The data sheet has some details about the "quiet zone". Is it wrong to violate the quiet zone in terms of nRD timing (as it probably would when connected to BUSY) as long as I make sure I ignore the data values present till it's outside this zone?

I essentially want to have 8 data lines and 1 clock (nCONVST) driving the ADC and making sure that the FPGA respects the timing requirements for data ready.

Thanks!