Hello All,

I am having a problem with a PCB running a DAC8568 on a shared SPI line driven by a MSP430F5438. The SPI is shared with a DAC8563 and two AD7689 ADCs. During the operation of our system the output of the DAC8568 drops to zero despite valid DIN, SCLK, and /SYNC signals coming in on the SPI lines. We are not using the nLDAC signal. The only way we have found to restore the output of the DAC8568 is to reinitialize the DAC configuration settings over the SPI. The dropout is very intermittent and we have not been able to trace a clear root cause. The dropout occurs on multiple boards and is cleared by cycling power or reinitializing.

As a side note the DAC8563 does not dropout despite sharing a common DIN and SCLK. The SPI communication cycles around the 4 devices on the bus.

Are there any thoughts on what could be causing our dropout and how we can prevent the problem?

Thanks in advanced,

Darnell

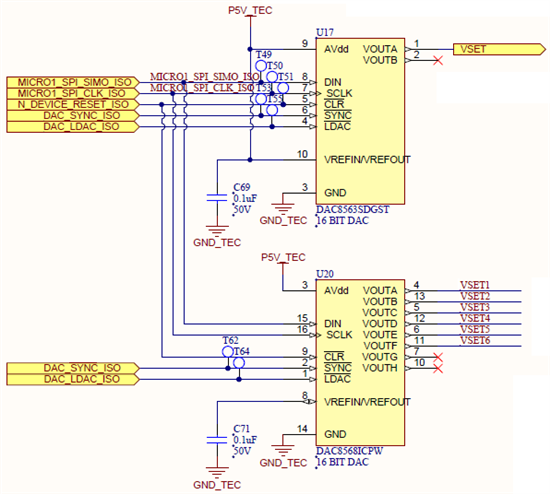

Connections to the DAC8568 in the schematic:

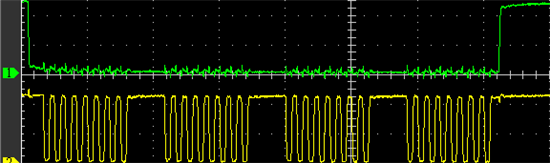

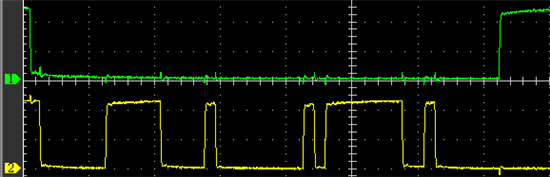

Scope captures of the DIN, SCLK, and /SYNC while the DAC is not outputting: