Hi Team,

I would like to ask you about DAC121C085 analog signal output timing.At which timing does the device outputs the analog data which is converted from the input digital data ? There were no timing chart in the datasheet which shows SCL, SDA,and VOUT.

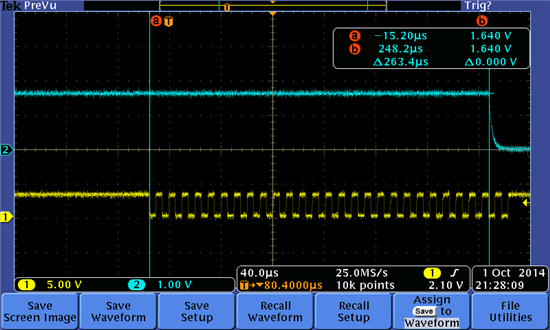

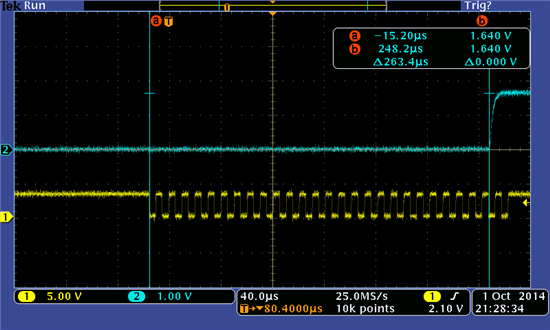

In our customer evaluation, VOUT starts to rise and output the analog data right after it receives the data, before the I2C NACK and STOP bits.

Is this the normal operation for DAC121C085 ?

Best Regards,

Kawai