Hi

I am trying to interface ADS1294 with STM32F4 using SPI.

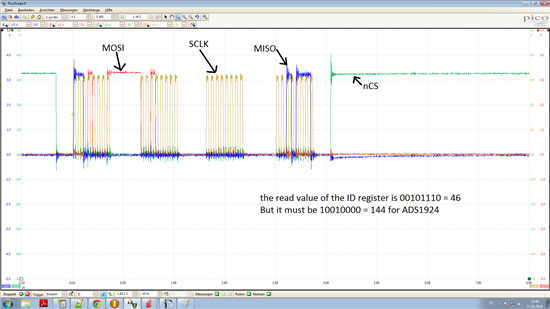

The problem is, that when I try to read the ID register, I allays get some different (wrong) value.

Here is my code:

void ads_read_from_register(adsRegister_t start_reg,

uint8_t number_of_reg_to_read, uint8_t *return_buff) {

uint16_t i, p;

CS_ADS_LOW;

//send SDATAC command

SPI_tx_rx_8bit(ADS_SPI, ADS_SDATAC);

//send RREG command and start address

SPI_tx_rx_8bit(ADS_SPI, (ADS_RREG | start_reg));

//send number of registers to read

SPI_tx_rx_8bit(ADS_SPI, (number_of_reg_to_read - 1));

for (i = 0; i < number_of_reg_to_read; i++) {

return_buff[i] = SPI_tx_rx_8bit(ADS_SPI, 0);

}

CS_ADS_HIGH;

}

void ads_init(void) {

uint32_t i;

//SPI initializations

ads_low_level_init();

i = 9000000;

while (i--)

; //wait

//activate ads1294

ADS_nPWDN_HIGH;

ADS_nRESET_HIGH;

i = 9000000;

while (i--)

; //wait

//perform reset

ADS_nRESET_LOW;

i = 9000000;

while (i--)

; //wait

ADS_nRESET_HIGH;

ADS_START_HIGH;

ads_read_from_register(ID, 20, &ads_reg[0]);

}

As you can see from above:

* nRESET is HIGH

* nPWDN is HIGH

* START is HIGH

* I want to use the internal clock of the chip so i set CLKSEL also to HIGH (this is done in the ads_low_level_init() )

* before i send RREG command i send SDATAC command

* in the next byte I send the number of registers to read -1

* after that a send number of registers to read -1 bytes in order to get the register content

As mentioned above the read value of the ID register is aways different.

I also checked the nDRDY line - I see peeks with period of 4ms so I guess the chip is running.

Please check also the scope screen shot

SPI configuration:

* CPOL=0 CPHA=1

* f_sclk = 10.5 MHz

best regards,

Stefan