Hello,

I've had a rather dismal experience using the ADCPro software with the ADS1278EVM. It keeps crashing, but more specifically, the clock settings seem to be all screwed up.

1. When you start, the default settings are:

Data Rate (DR): 128.001k

Clock Frequency (CF): 32.768M

Modulator Frequency (MF): 8.192M

2. If I select High Res and then select back to High Speed mode, the settings are now:

DR:105.469k CF:27M MF:6.75M

3. Now if I select Low Power mode:

DR:52.734k CF:27M MF:3.375M

4. Now select CLKDIV=0:

DR:52.734k CF:13.5M MF:3.375M

5. Select High Speed mode: (CLKDIV automatically goes to 1)

DR: 52.73 CF:13.5M MF:3.375M

6. Select Low-Power mode again:

DR:26.367 CF:13.5M MF:1.6875M

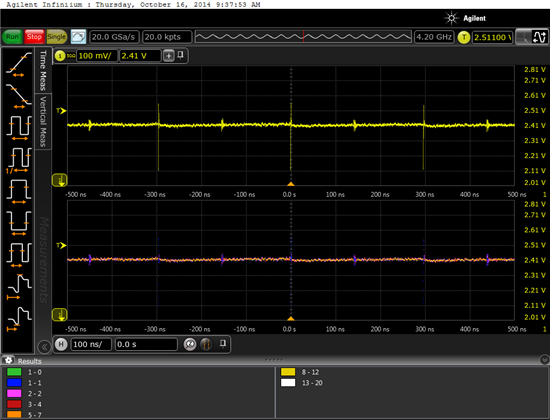

So now the data rate is different, even though it's the same configuration as (3). Screenshot from scope for this final configuration suggests that the modulator frequency is actually 3.375MHz.

I spent a lot of time trying to figure out why the numbers weren't matching up and went through the trouble of setting up this fancy scope, so fix it, please?

-Mike