Hi,

I want to daisy-chain two TLV5630 DAC's.

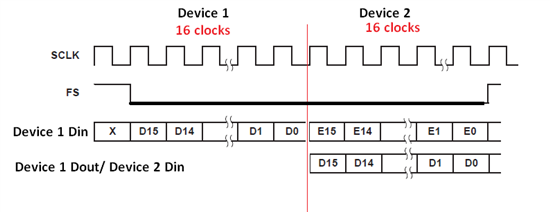

In the manual page 10 I read "For daisy-chaining, DOUT provides the data sampled on DIN with a delay of 16 clock cycles.". However, how do you acces DAC outputs 9 - 16? If the DOUT just feeds trough the data bits channel 1 of DAC 1 & 2 have the same outputs?

Thanks in advance,

Kevin