Hi,

I would like to ask you a basic question about ADC128S052 fsclk spec.

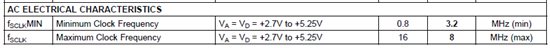

The specification is as below.

I think TI garantees min 3.2MHz and max 8 MHz, so I also suppose we cannot use the frequency between 0.8MHz to 3.2MHz and between 8MHz and 16MHz.

I do not understand why there is such specification on the datasheet.

Could you tell me what situation we can use out of from 8MHz to 3.2MHz?

Thank you in advance.

Best Regards,