Hi TI Forum,

I am using AD1278EVM REV E for my thesis and I use MSP430F5529LP to read data from ADC by SPI. The settings are as following:

S2 on ADS1278EVM: High resolution, TDM Fixed,

CLK: 8MHz from SMCLK (pin2.2) of MSP430F5529,

SCLK: 8MHZ from SPI (pin2.7) of MSP430F5529,

I give the supplise from MSP430F5529LP (+5V and +3.3V and generate 1.8V using LM317 from +5V).

I connect the pins on ADS1278EVM and MSP430F5529LP by cables as in Figure (1)

I am using MSP430F5529 integrated USB module to send data to computer and read data using MATLAB.

Figure (1)

I have two problems:

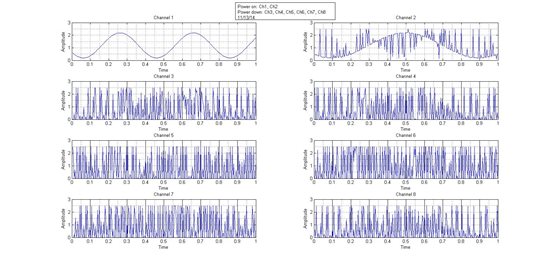

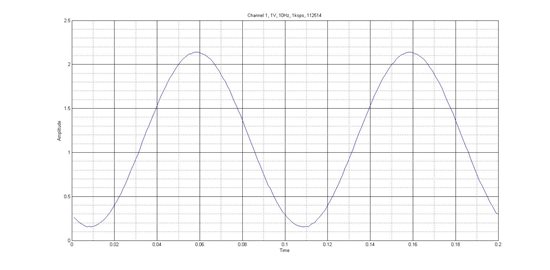

1. I try to read data from multiple channels . I apply 1V sin waves to channel 1 and channel 2 powering down all the other channels by S1. I receive the wrong output as in Figure (2). I expect channels 3 to 8 to be zero but they are not. In addition channel 2 is very noisy that I cannot apply signals with smaller amplitude.

Figure (2)

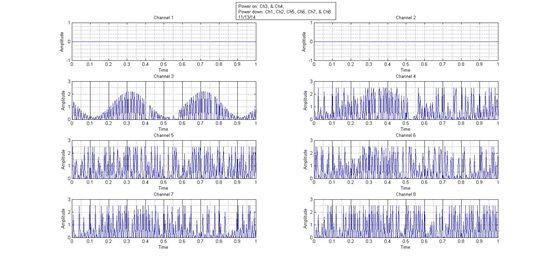

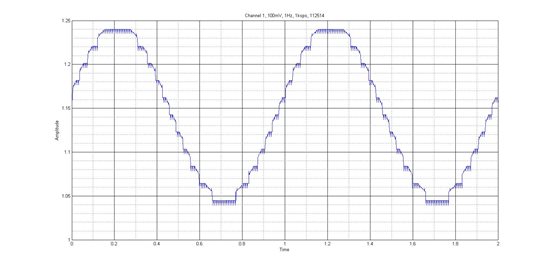

Then I apply the same signals to channels 3 and 4 powering down the remaining by S1 (Figure 3). This time channels 1 and 2 are ok giving right output (zero) but channels 5 to 8 behave the same way. In addition data from channels 3 and 4 are very noisy that in channel 3 I can only see envelope of the input signal and in channel 4 it is barely recognizable.

Figure (3)

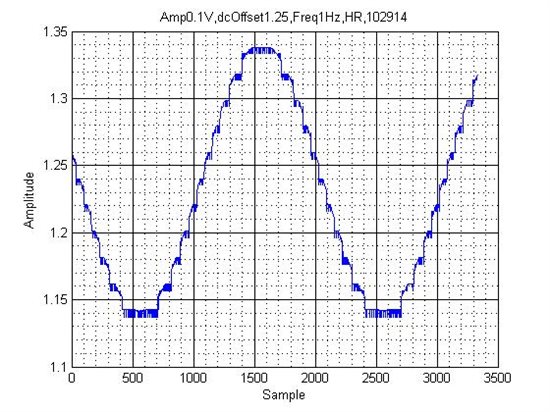

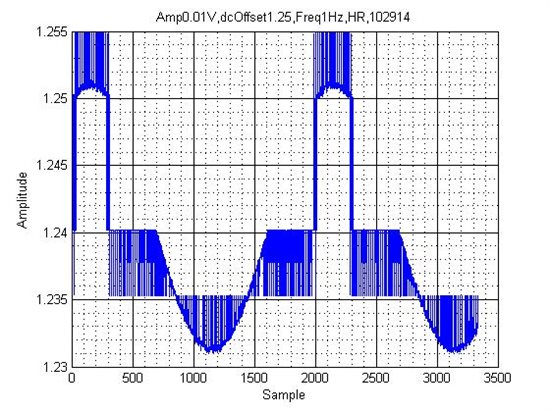

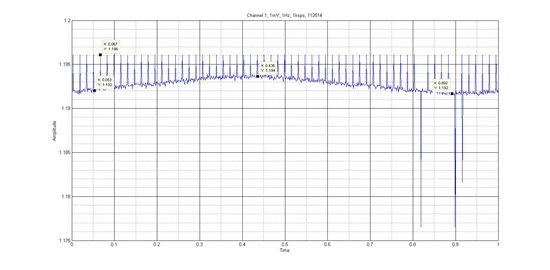

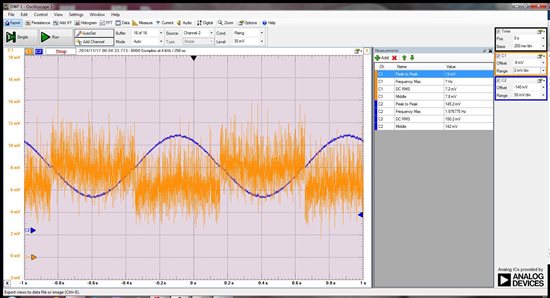

2. My second problem is with small amplitudes and lower frequencies. I need this device to detect signal about 1mVp-p and frequency of 1Hz. As I decrease amplitude and frequency I come up with the problem in Figure (4) and Figure (5). Inputs are 100mV, 1Hz and 10mV, 1Hz respectively.

Here is the section of the code I am using to read data through SPI:

UCA0CTL1 |= UCSSEL_2 + UCSWRST;

UCA0CTL0 |= UCCKPL + UCMSB + UCMST + UCSYNC ;

UCA0BR0 |= 1;

UCA0BR1 &= 0;

UCA0MCTL = 0;

UCA0CTL1 &= ~UCSWRST;

while(1)

{

for (counter = 0; counter < 24; counter++)

{

UCA0TXBUF = TX_Data;

while (!(UCA0IFG && UCRXIFG));

DataBuffer[counter] = UCA0RXBUF;

}

}

Thanks

Reza

11/13/14