Dear Christopher,

Since our last contact I have the opportunity to make some progress in my application.

I still have some open issues and I want to share my doubts and some conclusions as well.

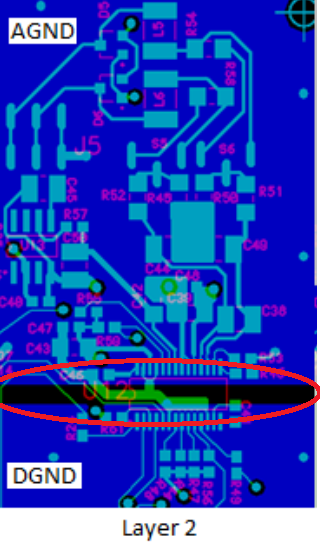

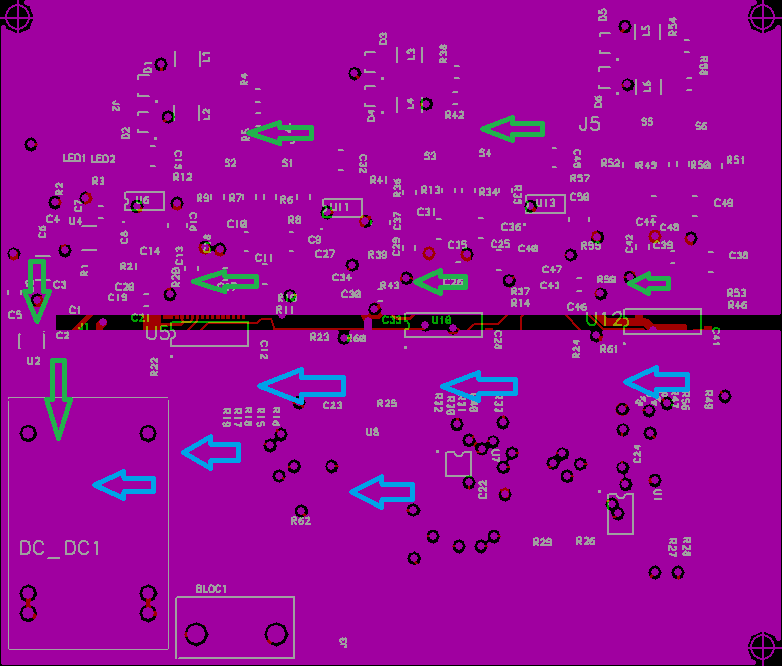

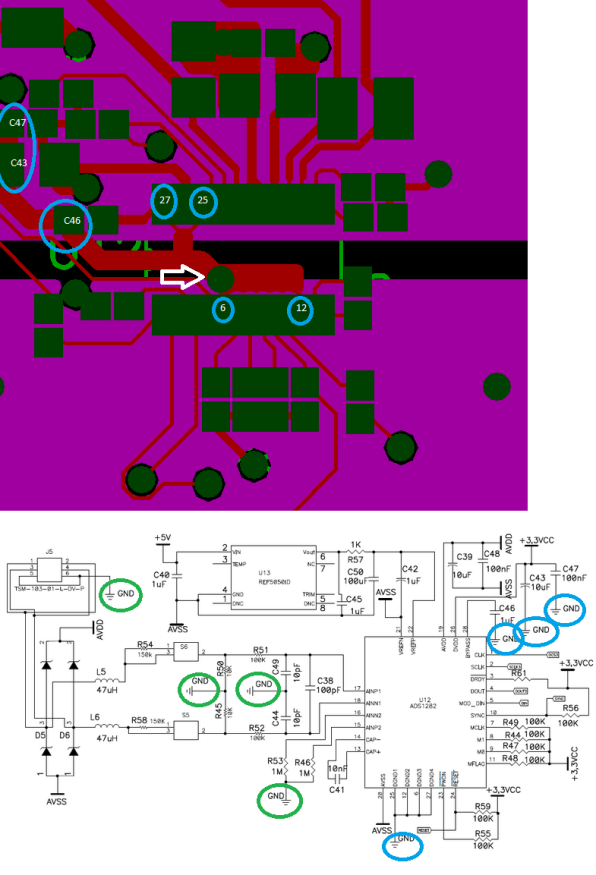

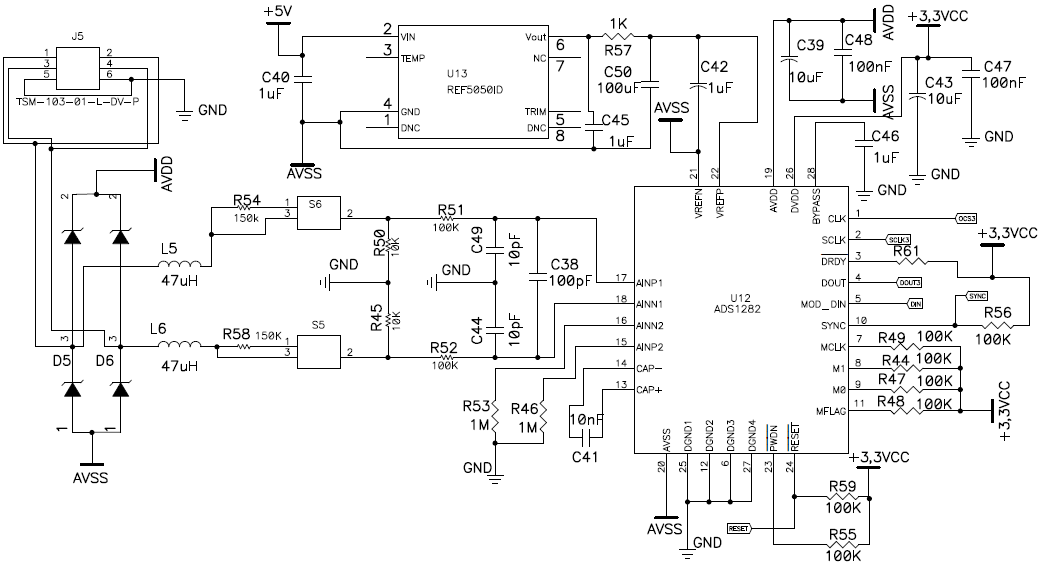

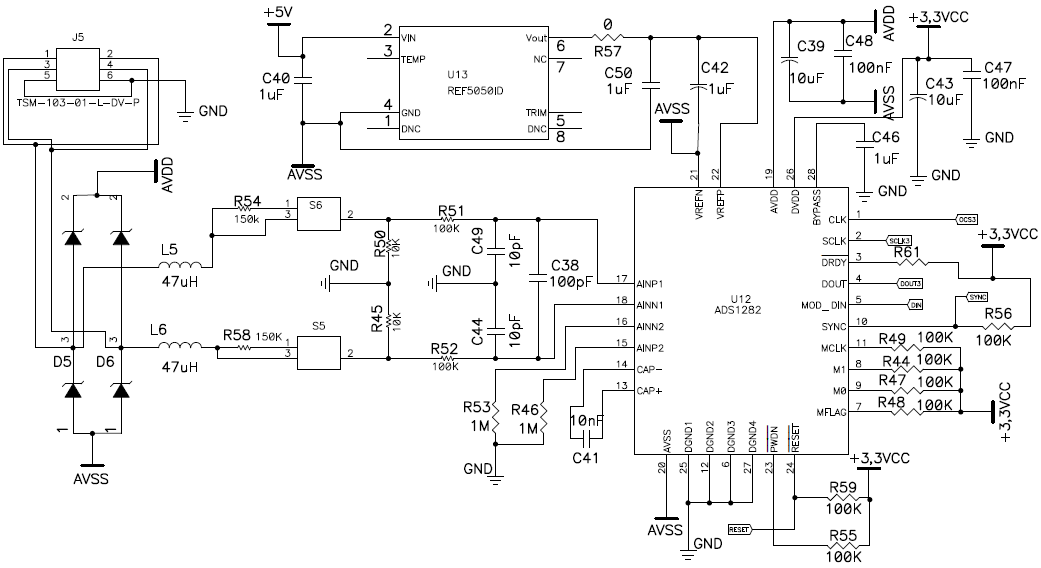

Before show you some DC and AC Analysis for different tests I suppose it’s important to give you an overall of the input circuit diagram and pcb layout used in this first prototype.

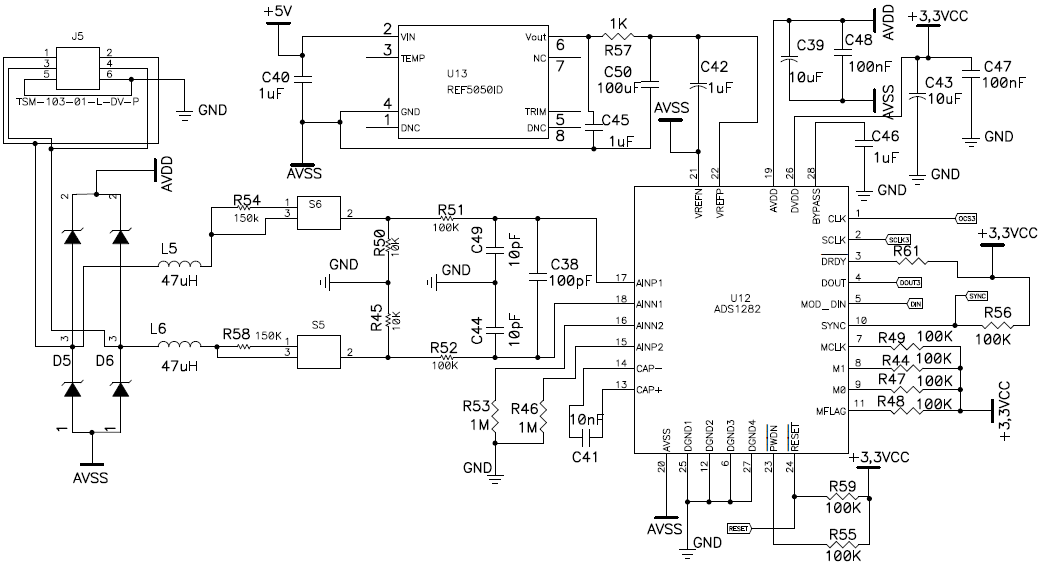

In the picture below you can see the electrical diagram of one channel (input circuit, AD converter, REF5050 …)

Picture 1 – Input 3 diagram

AVDD and AVSS are provided by TPS79225 (+2,5V) and TPS72325 (-2,5V), and a DC-DC converter (+-5V) is used to feed those regulators and other peripherals in the entire circuit.

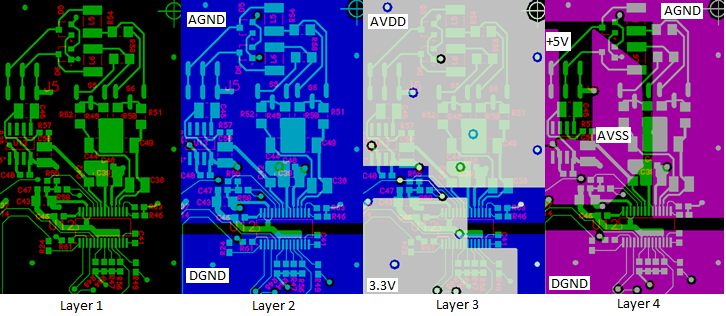

In the picture below you can see the pcb layout layer by layer for the input diagram (Picture 1). PS.: In the layout below please disconsider C45 from the pads connecting REF5050 Pin5 (TRIM) and AVSS, and instead this I installed a 1uF C45 0603 capacitor between REF5050 Pin6 (Vout) and AVSS like the input diagram (Picture 1).

Picture 2 – Input 3 PCB Layout

Question 1:

Looking for the circuit diagram and pcb layout there’s something I could change to improve my circuit performance? I’ll show you some AC and DC analysis latter.

Question 2:

In our last contact I told you I intended to use the network (R54, R50, R54, R58) as an attenuator with a factor of 1/16 because the sensor output range (+-20V) can decrease the signal amplitude to +-1.25V to match the ADS1282 PGA input operating range (AVSS + 0.7; AVDD – 1.25). Is this range true or I can use a signal range from -2.5V to +2.5V? The reason I want know is because my Vref = 5V (Vrefp= +2,5; Vrefn = -2,5), so limiting my input signal from -1.25 to +1.25, I’ll lost resolution from my ADC. In this case should I use a PGA multiply factor 2 to match the desired ADC input range (+-2.5V), I think if I use a factor 2 for 250SPS I’ll get almost the same performance as I use a factor 1?

Question 3:

Should I use the RC filter (R57, C50) after the output of REF5050? The reason is because this resistor in series with the ADS1282 Vref input impedance cause voltage attenuation, measuring with a true RMS multimeter I found +2.450V between Vrefp pin and GND instead of +2,50V from the REF5050 Vout pin.

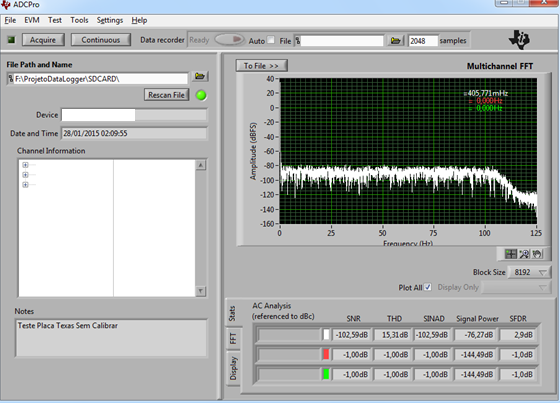

Questions regarding circuit evaluation using ADCPro (ALL TESTS PERFORMED USING Vrefp = +2.5V, Vrefn = -2.5V, 250 SPS, HIGH-RESOLUTION, LINEAR-PHASE, SYNC + LPF filter, AINP1 & AINN1, PGA CHOPPING ENABLE, G = 1):

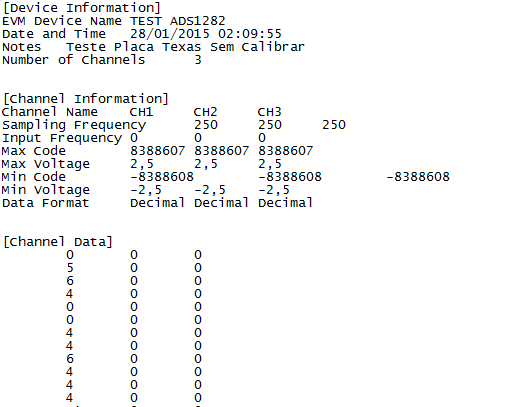

I used the AC and DC analysis from ADCPro software to evaluate my circuit and the first problem I found was to adapt the results in a spreadsheet file format that ADCPro could read and evaluate the results.

Unfortunaly during the first test I discovered ADCPro was not able to read 32bit integer values and interpret the results, so I decided to divide each sample by 256 to represent only 24bit integer values (Max Code 8388607, Min Code -8388608) as you can see in the picture below. Doing in this way ADCPro was able to evaluate the results.

Picture 3 – ADCPro file format

Question 4: Is there a way to allow "ADCPro File Reader", read and evaluate 32bit integer value samples?

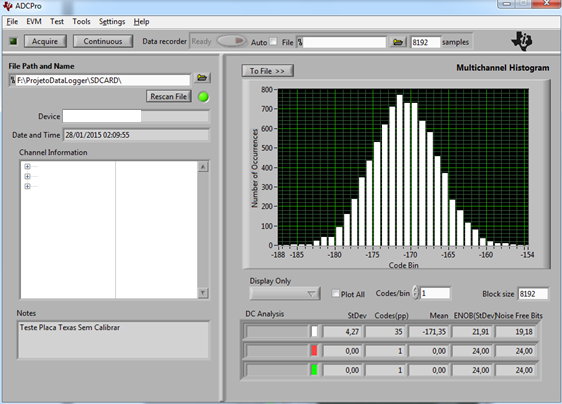

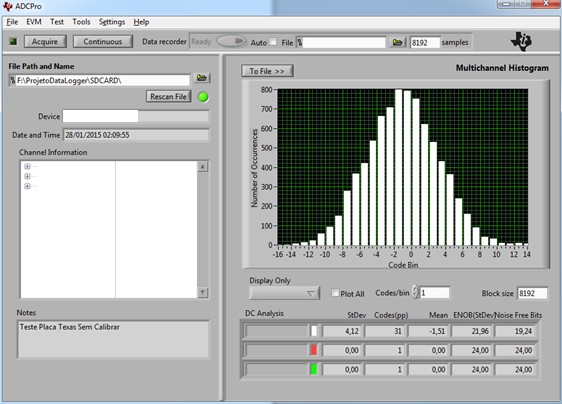

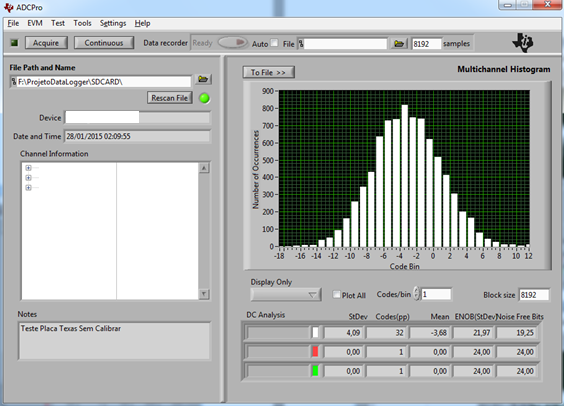

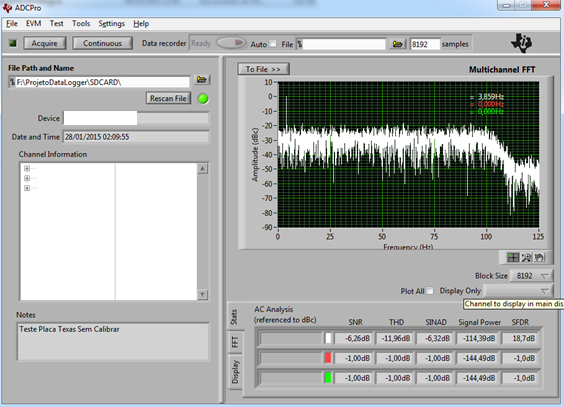

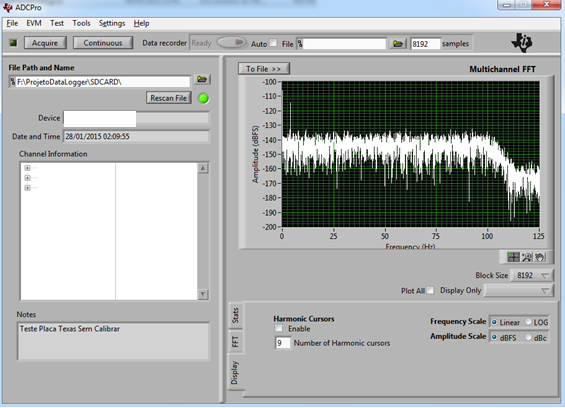

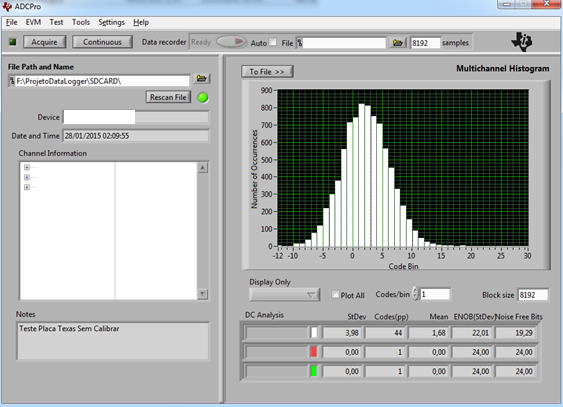

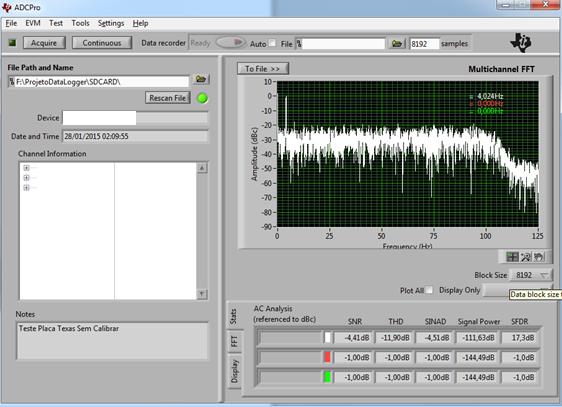

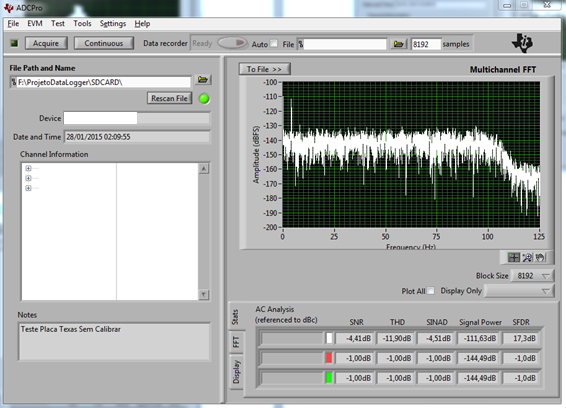

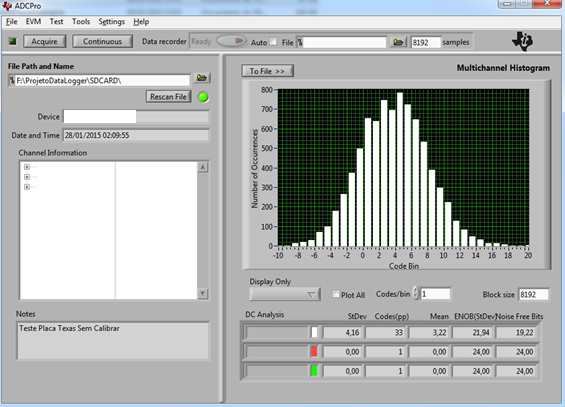

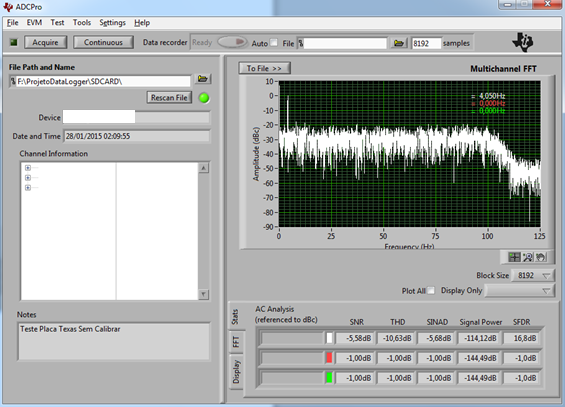

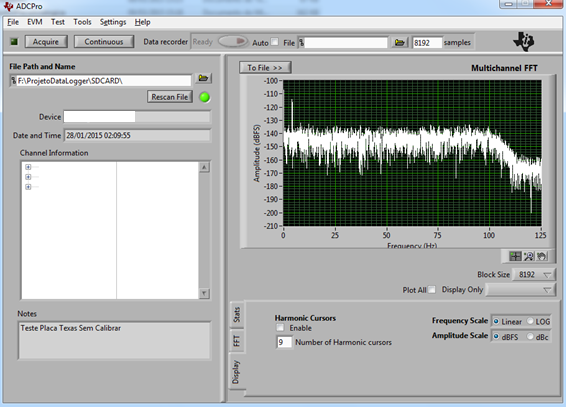

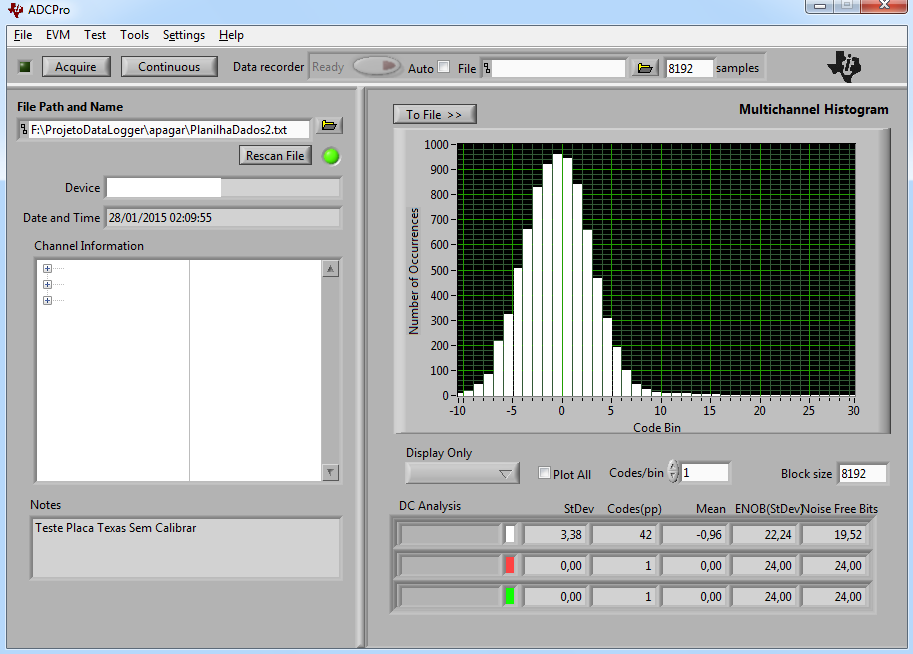

The first test I performed was without any calibration (Gain/Offset), no attenuation (R54, R58 bypassed by switches S5 and S6), shorted input Pins 1 and 3 of J5. In the next pictures you can see the AC and DC Analysis from the first test.

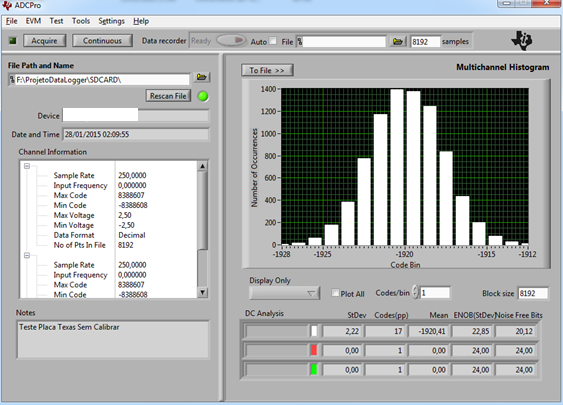

Picture 4: DC Analysis 1st test

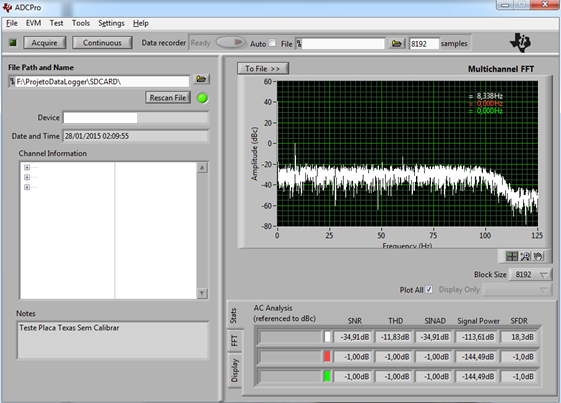

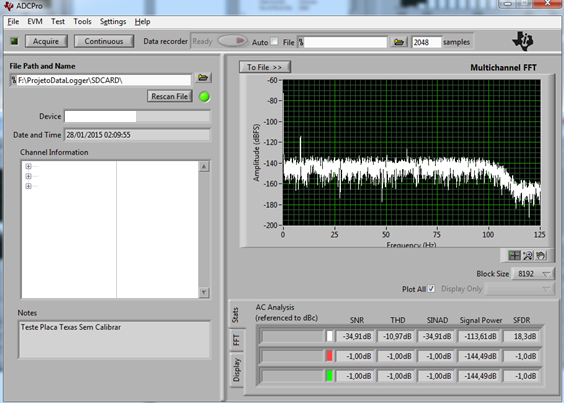

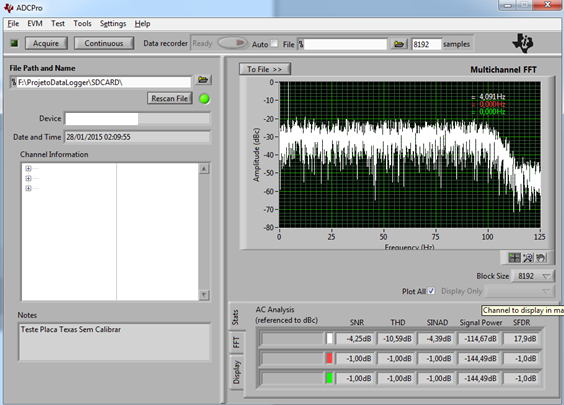

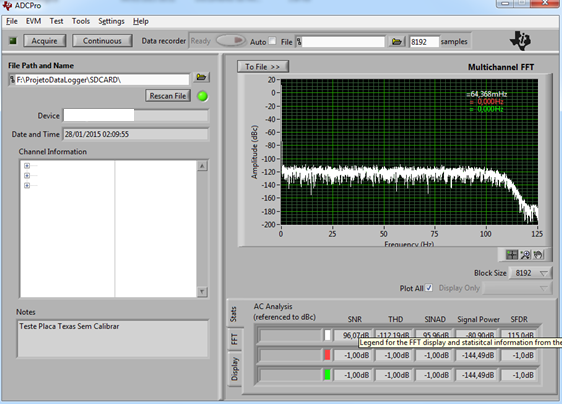

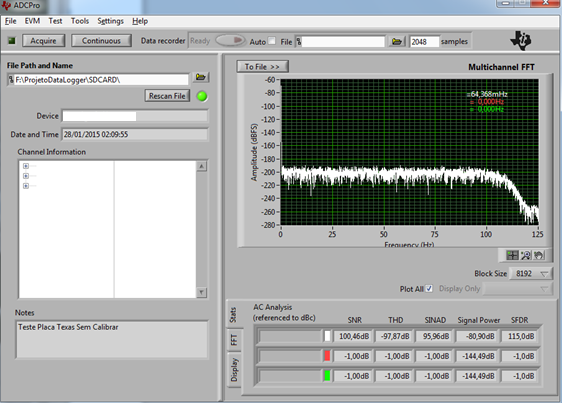

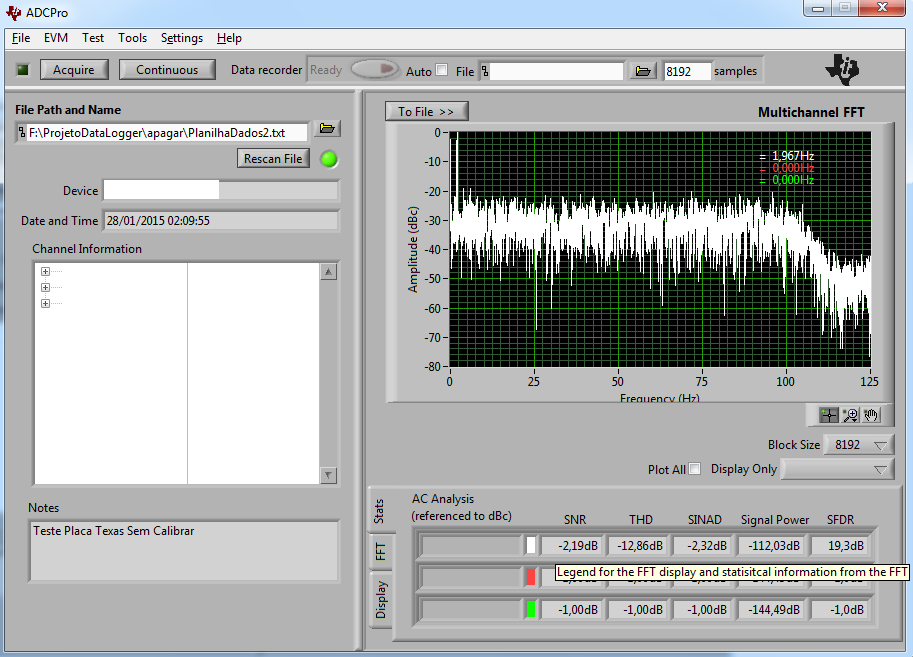

Picture 5: AC dBc Analysis 1st test

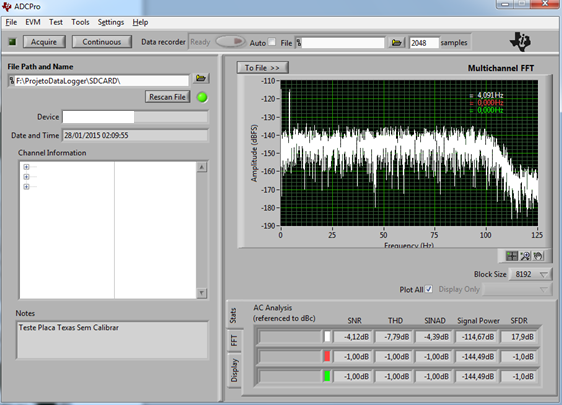

Picture 6: AC dBFS Analysis 1st test

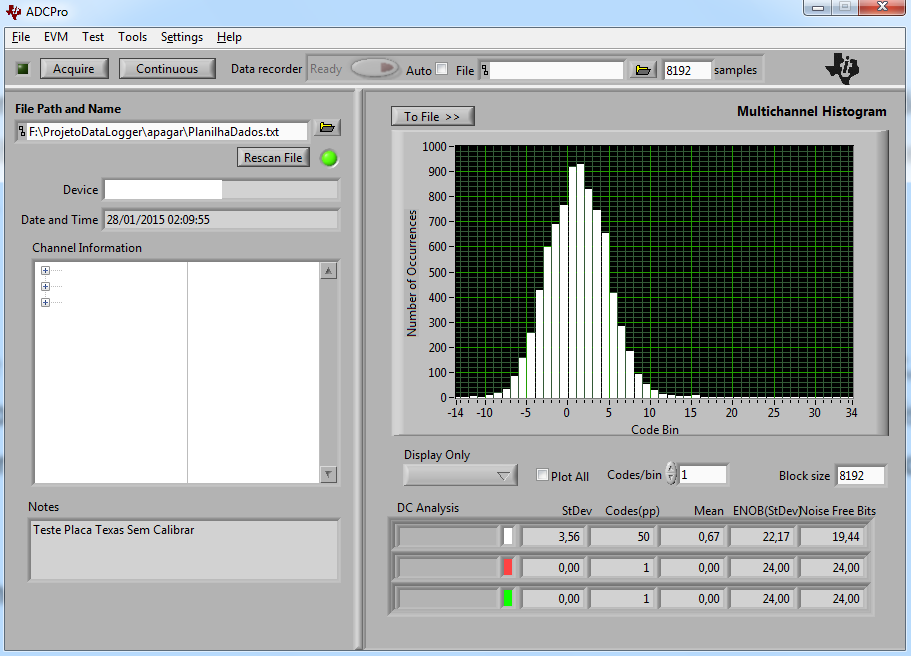

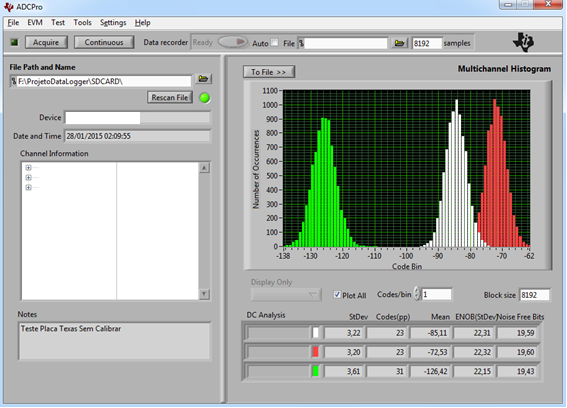

Question 5: Is there any possibility to improve the actual ENOB (21.91)? I did the same test with Texas ADS1282EVM board and reach the following results:

Picture 7: DC Analysis ADS1282EVM

Question 6: Could you help me to understand the results from the Picture 6? As I can see in the ADS1282 datasheet page 6, the SNR of ADS1282 for a shorted input and 1000SPS reach 124dB, the SNR result in Picture 6 was -34,91dB, probably the difference between the 0Hz (DC) signal amplitude and the 8.338Hz component.

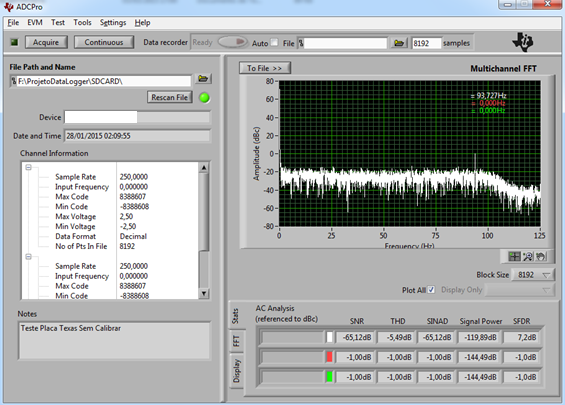

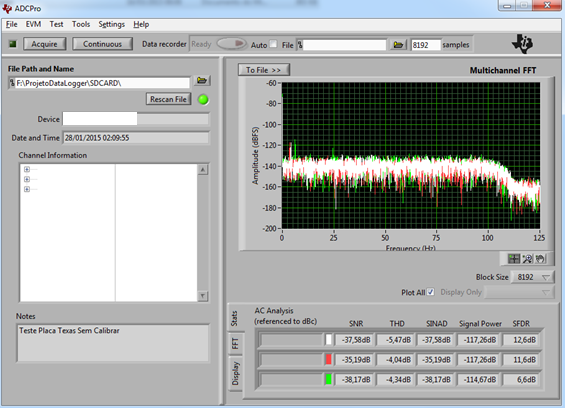

Question 7: When I performed the shorted input tests (250 SPS, unipolar Vref 0 – 5V) at the ADS1282EVM board I reach the following results (Picture 8), Is this correct? Why I have that component at 93.272 Hz? Is it correct the -65,12dB SNR (shorted input it means +2.5V Vocm at the AINP and AINN inputs?)?

Picture 8: AC dBc Analysis ADS1282EVM

The second test I performed after Offset calibration (OFC0 = ADh; OFC1 = FFh; OFC2 = FFh), no Gain calibration, shorted Pins 2 of S5 and S6. In the next pictures you can see the AC and DC Analysis from the second test.

Picture 9: DC Analysis 2nd test

Picture 10: AC dBc Analysis 2nd test

Picture 11: AC dBFS Analysis 2nd test

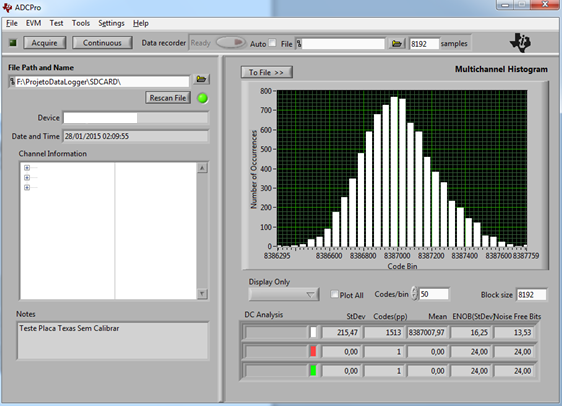

The third test I performed after Offset calibration (OFC0 = ADh; OFC1 = FFh; OFC2 = FFh) and Gain calibration Full Scale, using AVDD supplied by TPS79225 +2.5V(Vref/2) (FSC0 = 35h; FSC1 = D4h; FSC2 =50h). At this test I just connected the AVDD DC signal directly at the PIN2 of switch S6, and AGND at the PIN2 of switch S5, same procedure for the Full Scale calibration. I also measured the voltage using a true RMS multimeter, after the resistor R51 = 2.451V, before the resistor R51 = 2.495V. In the next pictures you can see the AC and DC Analysis from the third test.

Picture 12: DC Analysis 3rd test

Question 8: 1513 Codes(pp) it can be considerable a noisy power supply or not for this proposal?

Picture 13: AC dBc Analysis 3rd test

Picture 14: AC dBFS Analysis 3rd test

The fourth test I performed after Offset calibration (OFC0 = AAh; OFC1 = FFh; OFC2 = FFh) and Gain calibration Full Scale, using VREFP supplied by REF5050 +2.5V(Vref/2) (FSC0 = EFh; FSC1 = 4Fh; FSC2 =4Ch). At this test I just connected the VREFP DC signal directly at the PIN2 of switch S6, and AGND at the PIN2 of switch S5, same procedure for the Full Scale calibration. I also measured the voltage using a true RMS multimeter, after the resistor R51 = 2.196V, before the resistor R51 = 2.222V, this attenuation (2.5V to 2.222V) is mainly caused by the divider network (R57 = 1K and R50 = 10K). In the next pictures you can see the AC and DC Analysis from the fourth test.

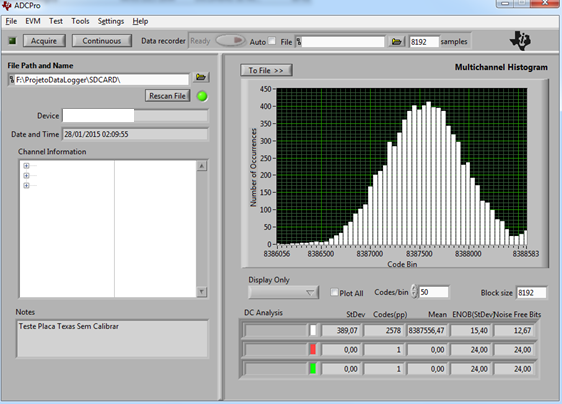

Picture 15: DC Analysis 4th test

Question 9: It seems to be very strange but if you compare the Histogram (Picture 15) with the Histogram (Picture 12), show us that the voltage reference supplied by REF5050 has much more noise in comparison to the one supplied by TPS79225. Is this correct? Why?

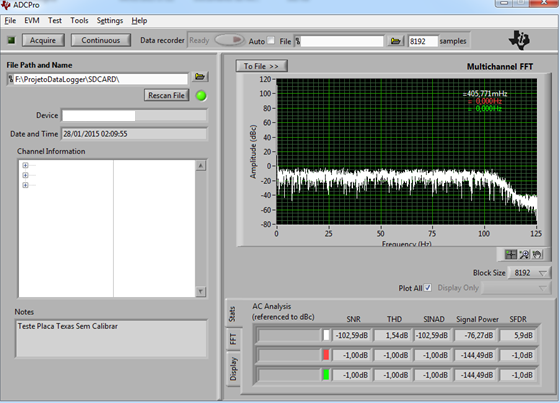

Picture 16: AC dBc Analysis 4th test

Picture 17: AC dBFS Analysis 4th test

If you need more information let me know, will be a pleasure to share.

Thank you in advance to share your experience!

Best Regards,

Flávio Cavalieri