Hi,

I am using software SPI in ATMEGA1281, built in module of MikroC PRO for AVR.

I am using following code, kindly let me know where I am making the mistake, please.

Thanks in advance with best regards.

sbit Chip_Select at PORTA5_bit; // Software SPI Chip Select

sbit SoftSpi_CLK at PORTA6_bit; // Software SPI CLK

sbit SoftSpi_SDI at PINA7_bit; // Software SPI Data In

sbit SoftSpi_SDO at PORTG2_bit; // Software SPI Data Out

sbit Chip_Select_Direction at DDA5_bit;

sbit SoftSpi_CLK_Direction at DDA6_bit;

sbit SoftSpi_SDI_Direction at DDA7_bit;

sbit SoftSpi_SDO_Direction at DDG2_bit;

void main()

{

int i;

unsigned short out_spi;

DDRA = 0x7F; // set direction to be output at Port A

DDRB = 0xFF; // set direction to be output at Port B

DDRC = 0xF0; // set direction to be output at Port C

DDRD = 0xFF; // set direction to be output at Port D

DDRE = 0xFF; // set direction to be output at Port E

DDRG = 0xFF; // set direction to be output at Port G

PORTB = 0x00; // PORTB Output

PORTD = 0x40; // PORTD Output

PORTE = 0x00; // PORTE Output

PORTG = 0x00; // PORTG Output

UART2_Init(115200); // UART Initialization at 115200 Baud Rate

Soft_SPI_Init(); // Init Soft_SPI

Delay_ms(20000); // Delay of 2second

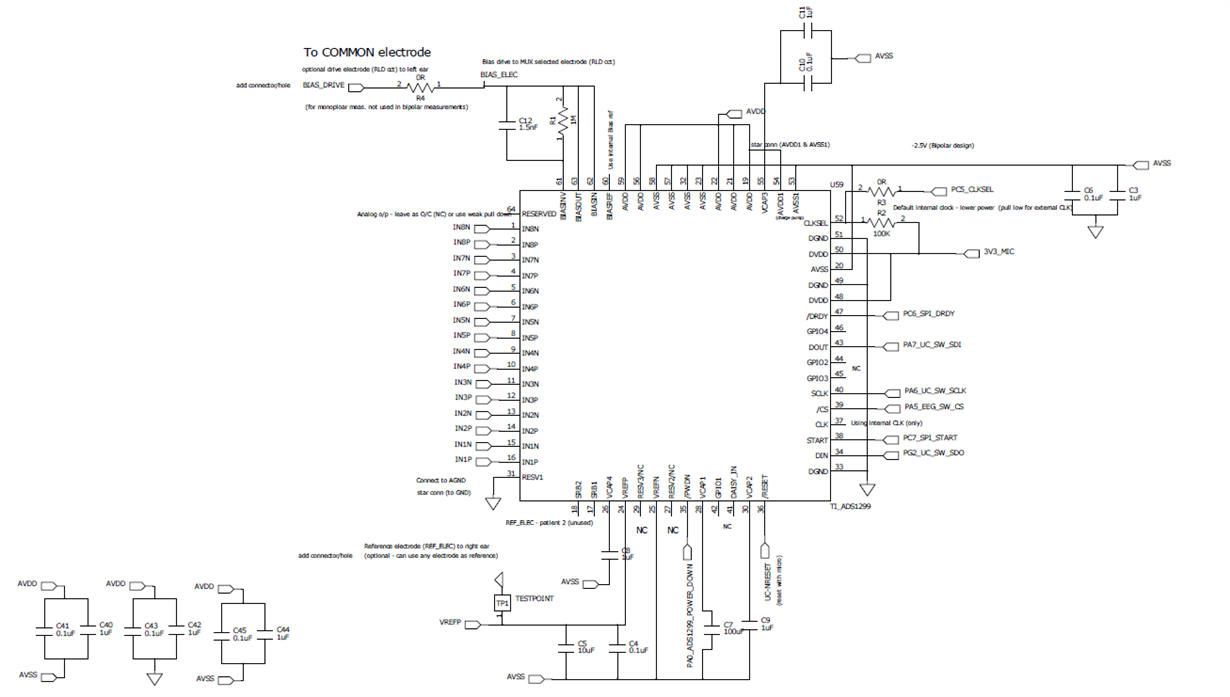

PORTC5_bit= 1; //CLKSEL=1 for internal Clock of ADS1299

Delay_ms(1000);

PORTC7_bit= 1; //START of ADS1299 set High

PORTA0_bit= 1; //PDWN of ADS1299

delay_ms(1200);

/* For Sequence detection*/

for ( i=0; i<10; i++)

{

UART2_Write_Text("A");

delay_ms(500);

UART2_Write_Text("B");

delay_ms(500);

UART2_Write_Text("C");

delay_ms(500);

}

PORTA5_bit= 0; // Chip Select of ADS1299

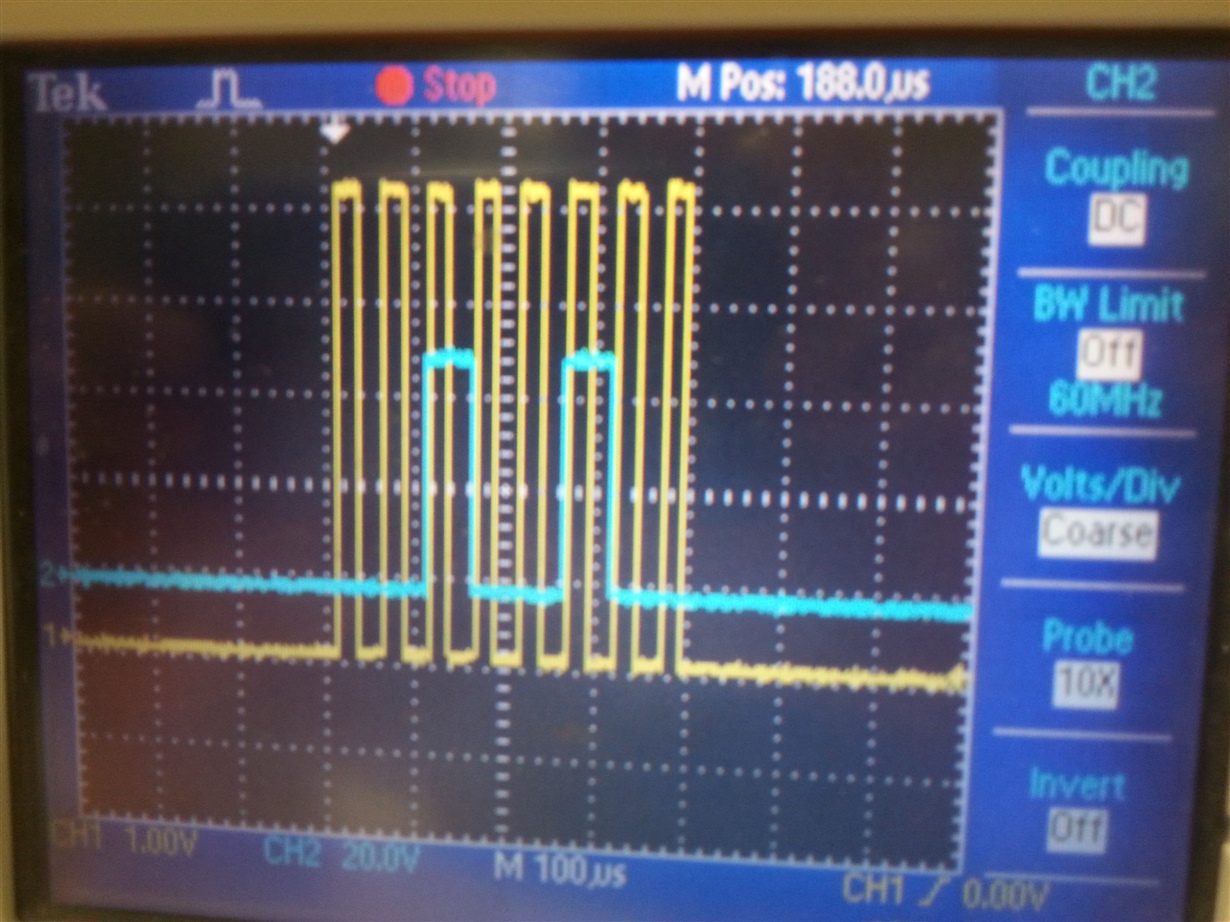

Soft_SPI_Write(0x88); //Data Mode

delay_ms(15);

PORTA5_bit= 1;

delay_ms(200);

/* ADS1299 Reset Setting*/

PORTA5_bit= 0; // Chip Select of ADS1299

Soft_SPI_Write(0x60); //Reset

delay_ms(15);

PORTA5_bit= 1;

delay_ms(200);

/* SDATA & RREG*/

PORTA5_bit= 0; // Chip Select of ADS1299

Soft_SPI_Write(0x88); // SDATA ADS1299

delay_ms(15);

PORTA5_bit= 1;

PORTA5_bit= 0;

Soft_SPI_Write(0x04); // RREG ADS1299

Soft_SPI_Write(0x00); // Ask for 1 Byte

delay_ms(15);

PORTA5_bit= 1;

do

{

PORTA3_bit= 1; // Debug LED1

PORTA1_bit= 0; // Debug LED2

Delay_ms(500);

PORTA5_bit= 0;

out_spi = Soft_SPI_Read(0x00); // Read ADS1299 ID

delay_ms(15);

PORTA5_bit= 1;

UART2_Write(out_spi);

delay_ms(5);

PORTA3_bit= 0; // Debug LED1

PORTA1_bit= 1; // Debug LED2

Delay_ms(500);

} while(1); // Endless loop

}