Hi all,

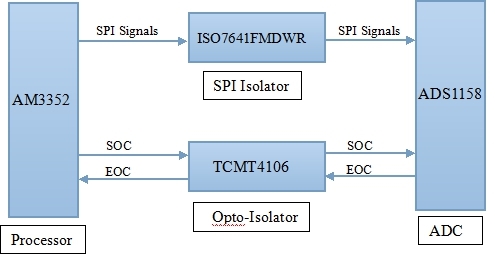

In one of our designs, we have used ADS1158 to measure the 8 analog inputs.

We have configured ADC in Auto Scan mode with 8 channels enabled.

The set data rate is 1075 SPS , thus the sampling period is approximately equal to 0.93 ms.

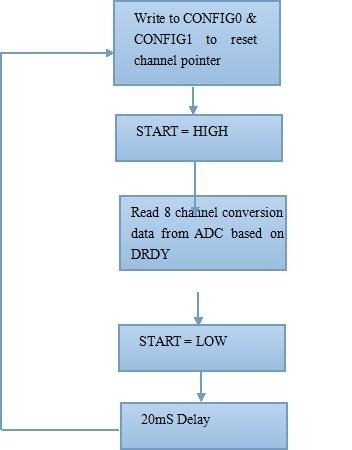

Below is the sequence of steps we are following for reading data from ADC:

1) Write to CONFG0 & CONFIG1 registers to reset the channel pointer

2) Make 'START' signal HIGH

3) Read 8 conversion data from ADC

4) Make 'START' signal LOW

5) Wait for 20mS

With the above configuration, we are facing some issues when tested for more than 24 hours.

We observed repetition in the channel data value of the ADC i.e any two consecutive channels read value will be same.

This error condition does not follow any pattern, basically it is random behavior.

From the ADC data sheet, we understands that Data out (DOUT) register of the ADC will be cleared after every read operation, and we don't find any possibility of reading the same data again for the next channel.

Can you please suggest any reasons for the above behavior over the long run test ?

Thanks,

Harsha