I've interfaced a CC2530 SoC EM with the ADS1278EMK and have written software to acquire readings from the ADS1278 over the SPI interface on USART2 and then forward those readings through the UART on USART1. I am in SPI-interface mode with TDM dynamic data. Everything is great with the 1st channel's reading but with the remainder of the channels I get a weird inverted bit issue.

The problem I have is that I am getting an inverted 24bit of the ADC reading at what seems to be randomly. In other words, a 0x00012D is being read as 0x80012D or a 0xFFF892 as 0x7FF892. The MSB is the only one that is ever affected with the rest of the bits ok. Again, this only happens for the channels 2-8, while channel 1 is always read in correctly.

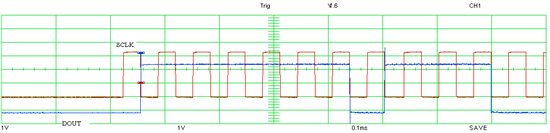

Is there a requirement that the duty cycle of the SCLK be maintained at 50%? (there is a small lag after each 8 clock cycles because I am using the SPI interface to provide the SCLK with byte transfers). Do I need use DMA transfers to reduce this lag? Any other potential issues?