Hello everybody

After going through datasheets and app notes again and again we would like to ask a question in this forum.

We are using an ADS1247 to measure 3 analog signals, thus we operate the ADC in single ended mode. The sampling rate is 5 SPS since we need high resolution. We are using the internal reference voltage of 2.048 V.

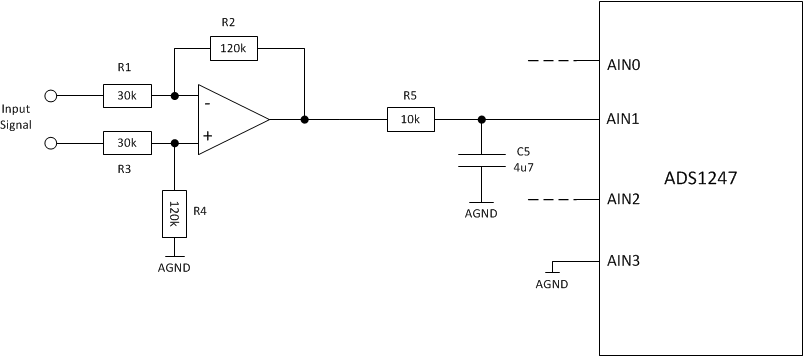

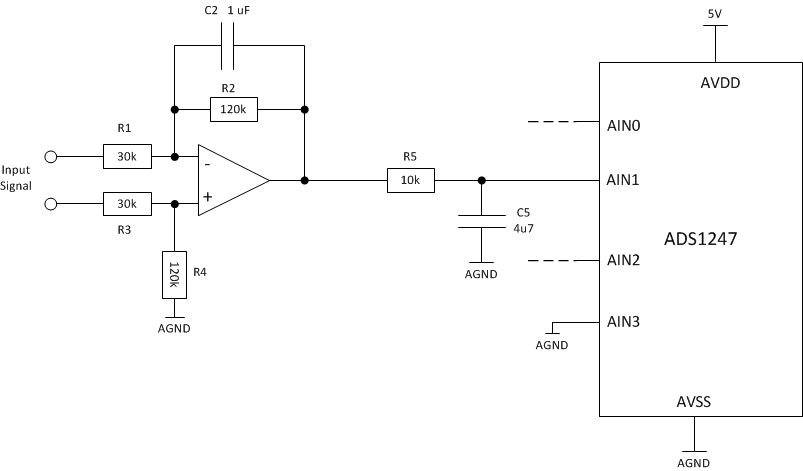

We also have an analog filter before the signal goes into the ADC to remove unwanted frequencies form the signal. It is also used as anti-aliasing filter.

In the schematic below just one channel (AIN1) is shown since the others are very similar.

Due to the filter's time constant of T = R5 * C5 = 10k * 4.7uF = 0.047 s = 47 milliseconds we expect the signal to stop drifting after 20 * T = 20 * 47 milliseconds = 940 milliseconds.

In order to check the step response we have made several experiments:

Experiment 1:

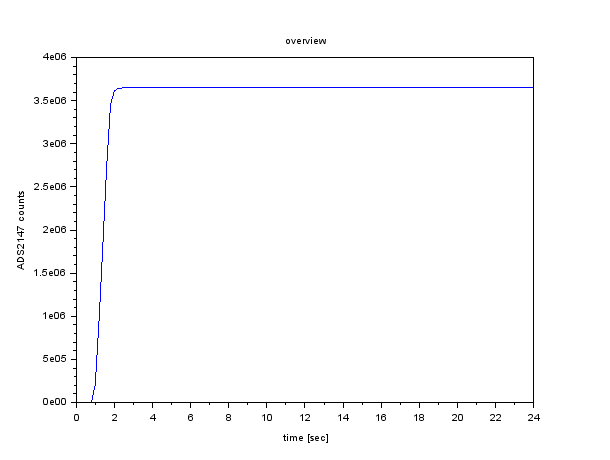

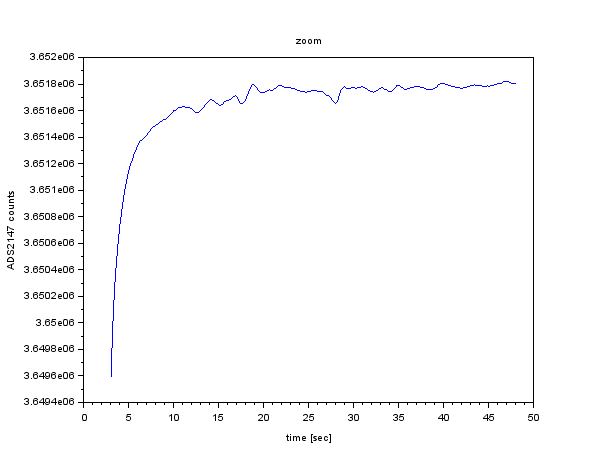

Apply a step and measure how long we can see signal drift in the converted AD values.

Result:

It takes about 6 seconds until the signal settles. W.r.t. the just calculated settling time above this is far too long.

When measuring the voltage over C5 then we exactly see the expected voltage curve!

Experiment 2:

Remove C5 to eliminate the low pass filter.

Apply a step and measure how long we can see signal drift in the converted AD values.

Result:

It takes about 2 seconds until the signal settles. This is more or less the expected behavior.

Questions:

-

Why do we have such a significant difference in the settling time?

-

When using an ADS1247 do we need to have an anti-aliasing filter before the ADC? Or is there already one included in the ADS1247 somewhere?

-

We know that there are capacitors in the ADS1247, do we have to consider them when connection external capacitors? May they interfere?

Thanks for your support already in advance

Best Regards

Yves