Hello TI Team,

I am using a controller that cannot send all 24 bits together over SPI but 8 bits 3 times. Does AMC7812 support it?

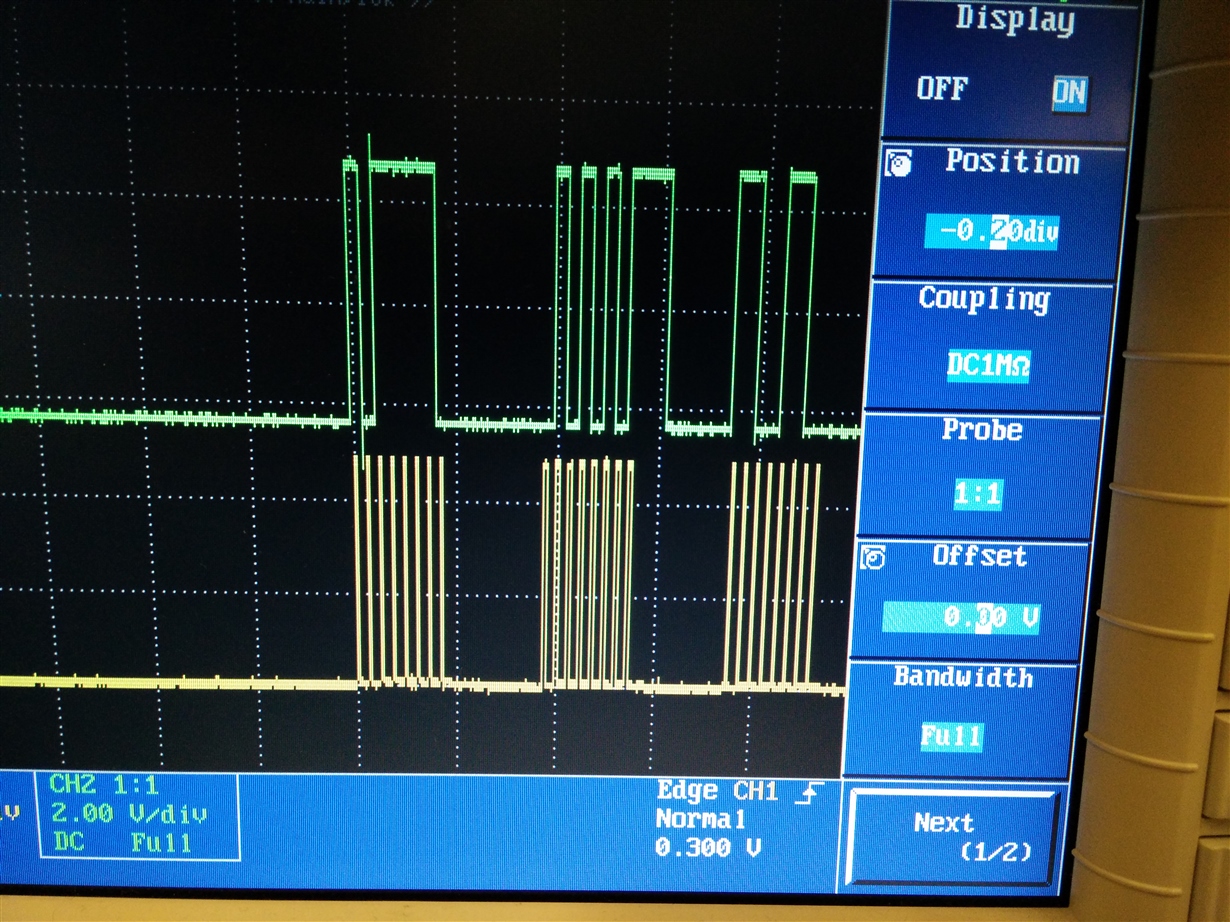

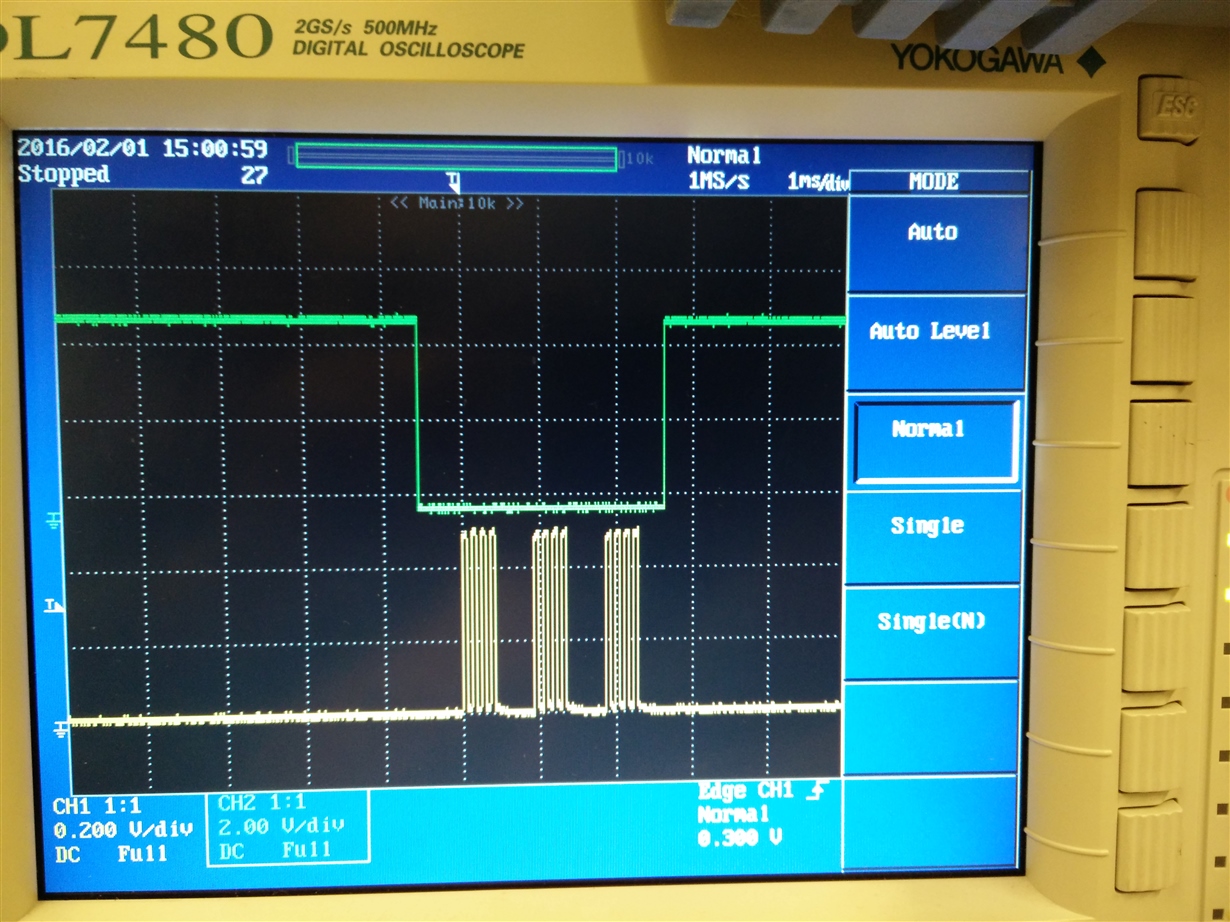

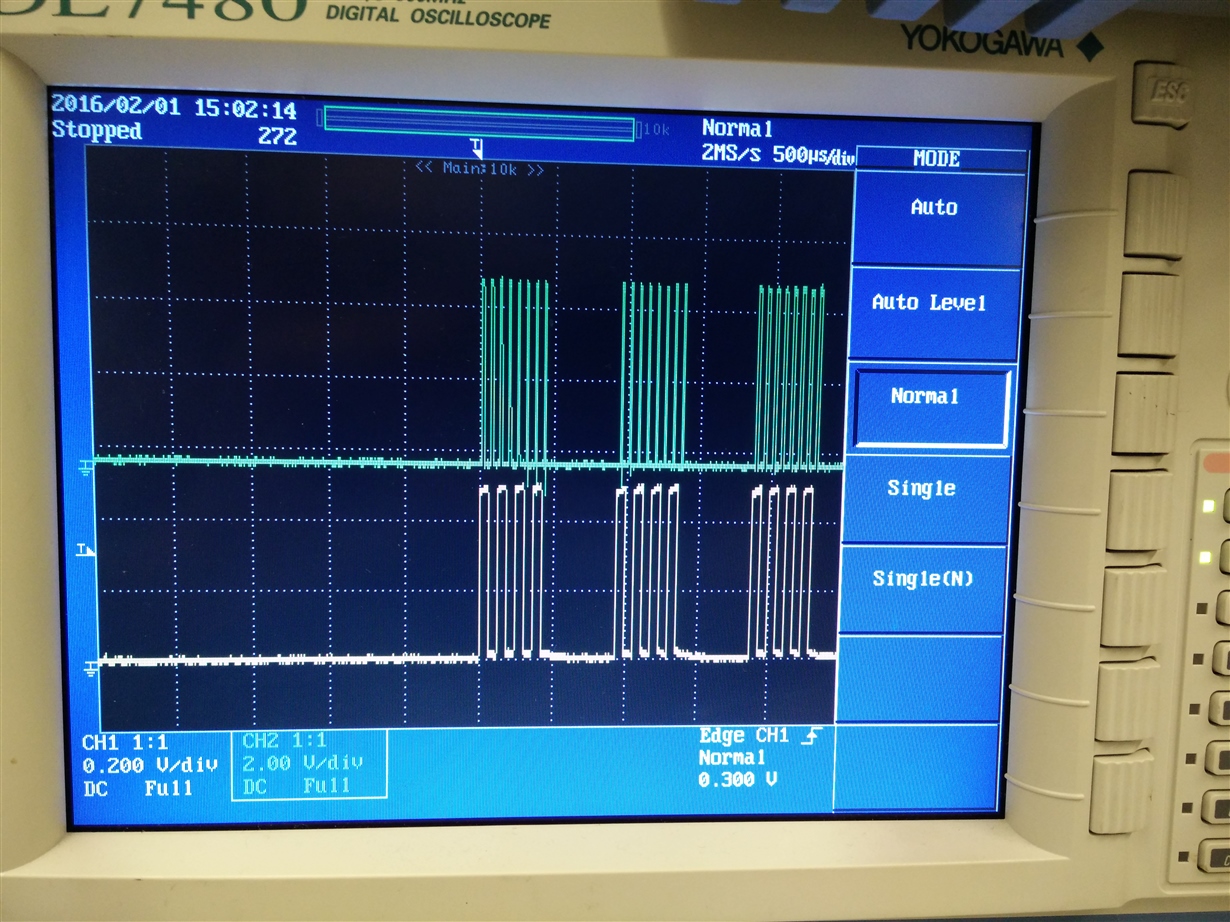

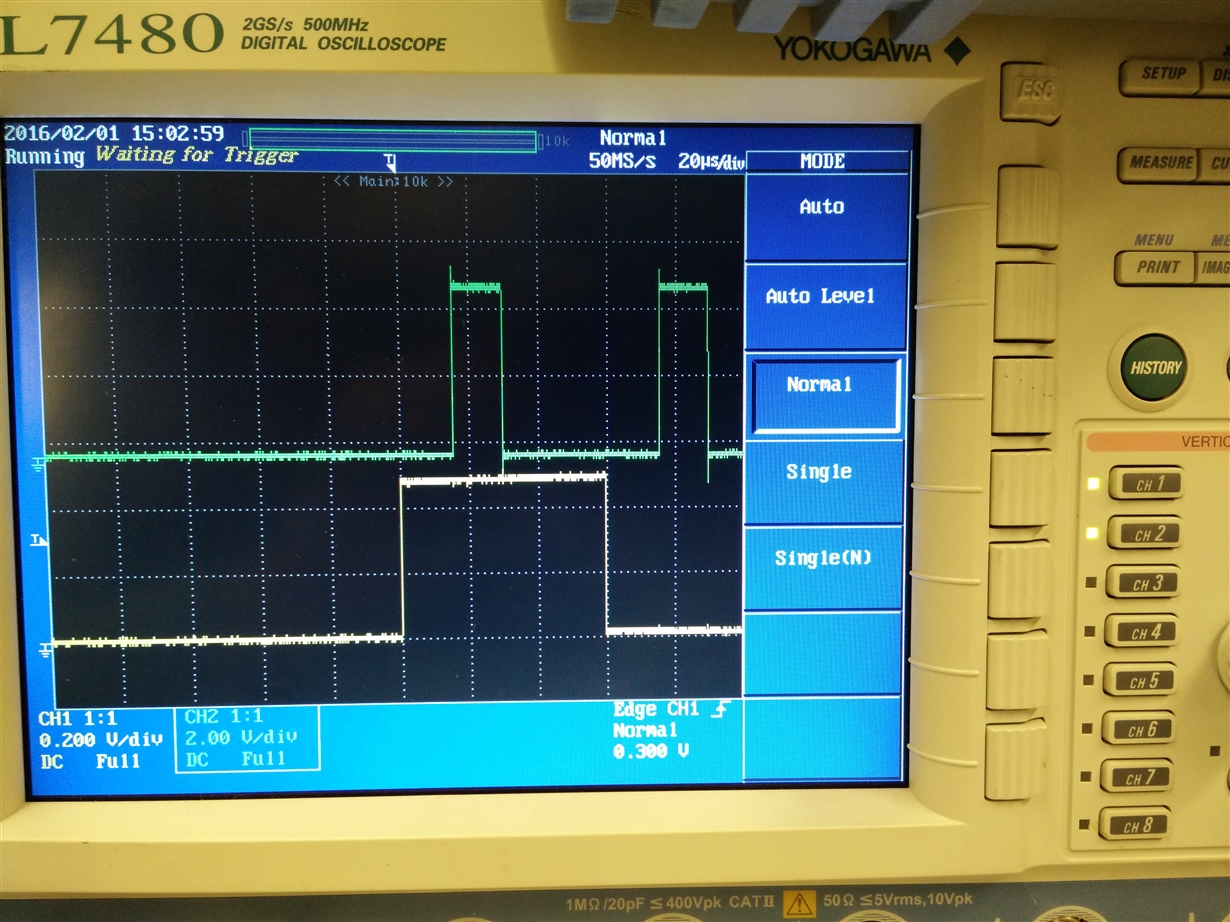

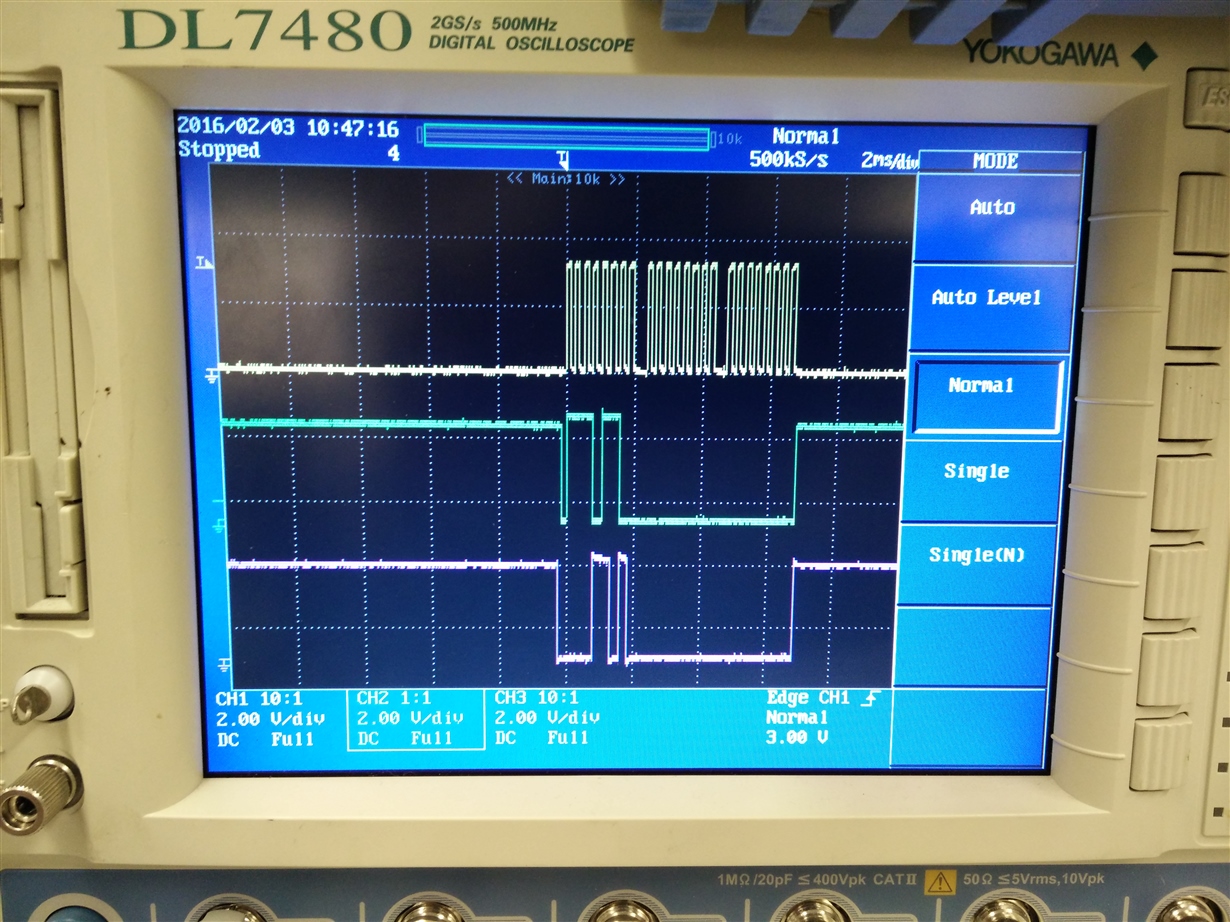

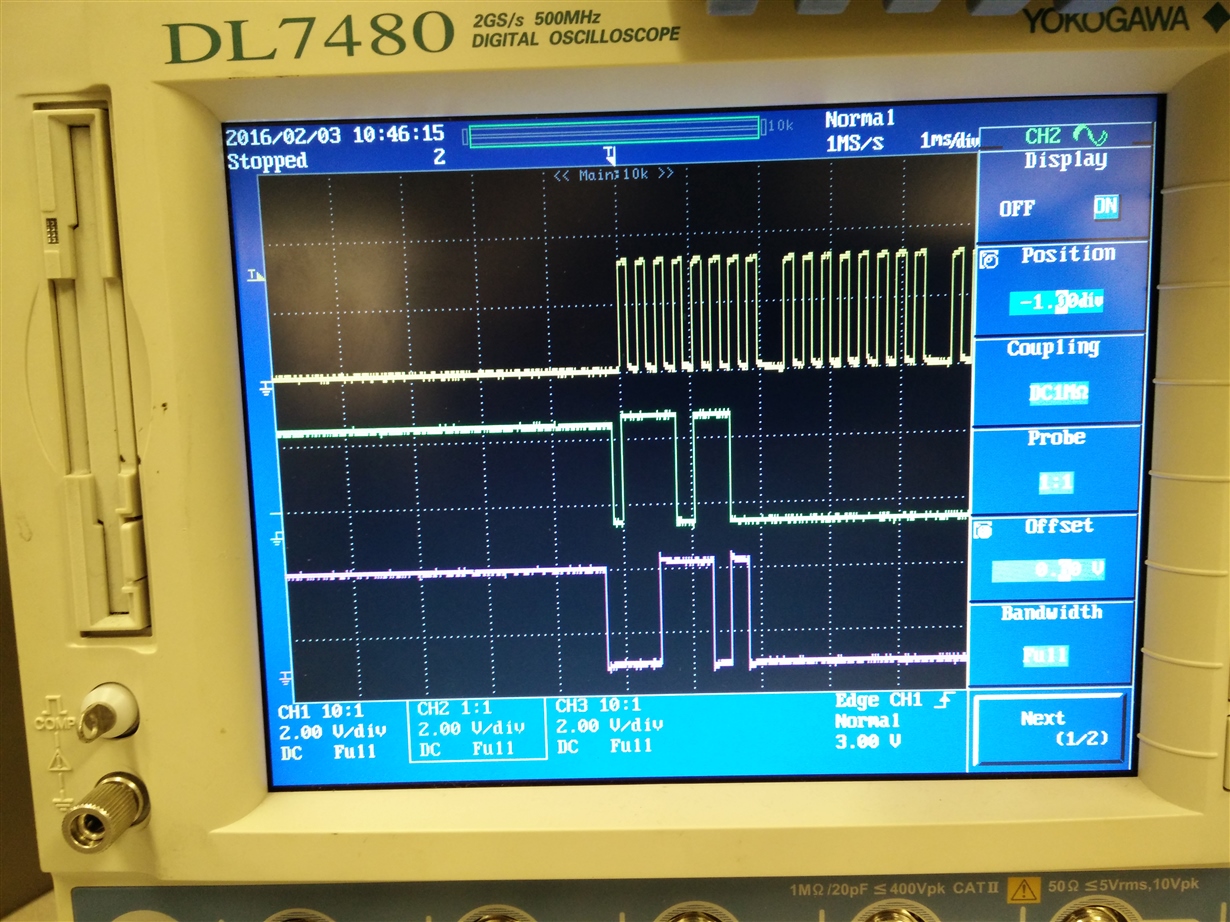

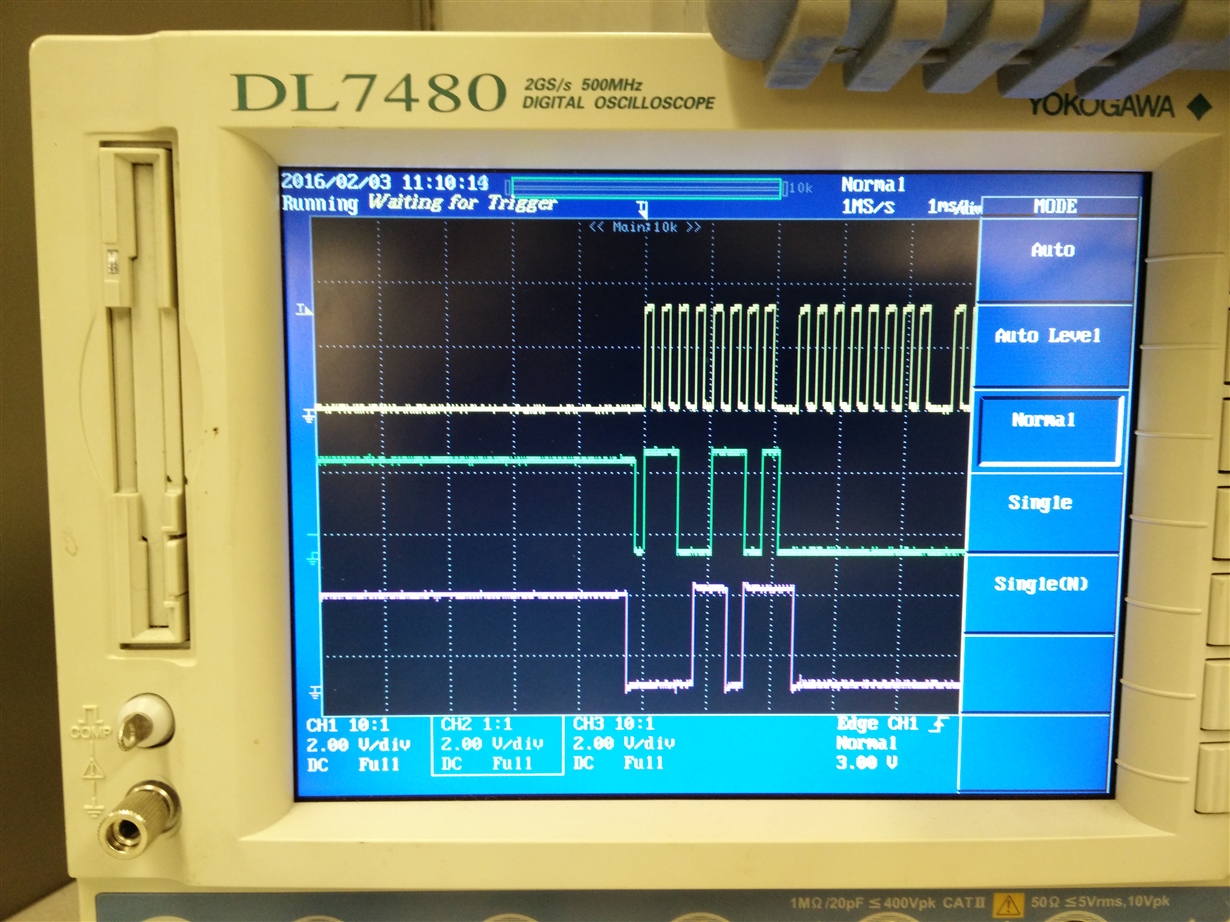

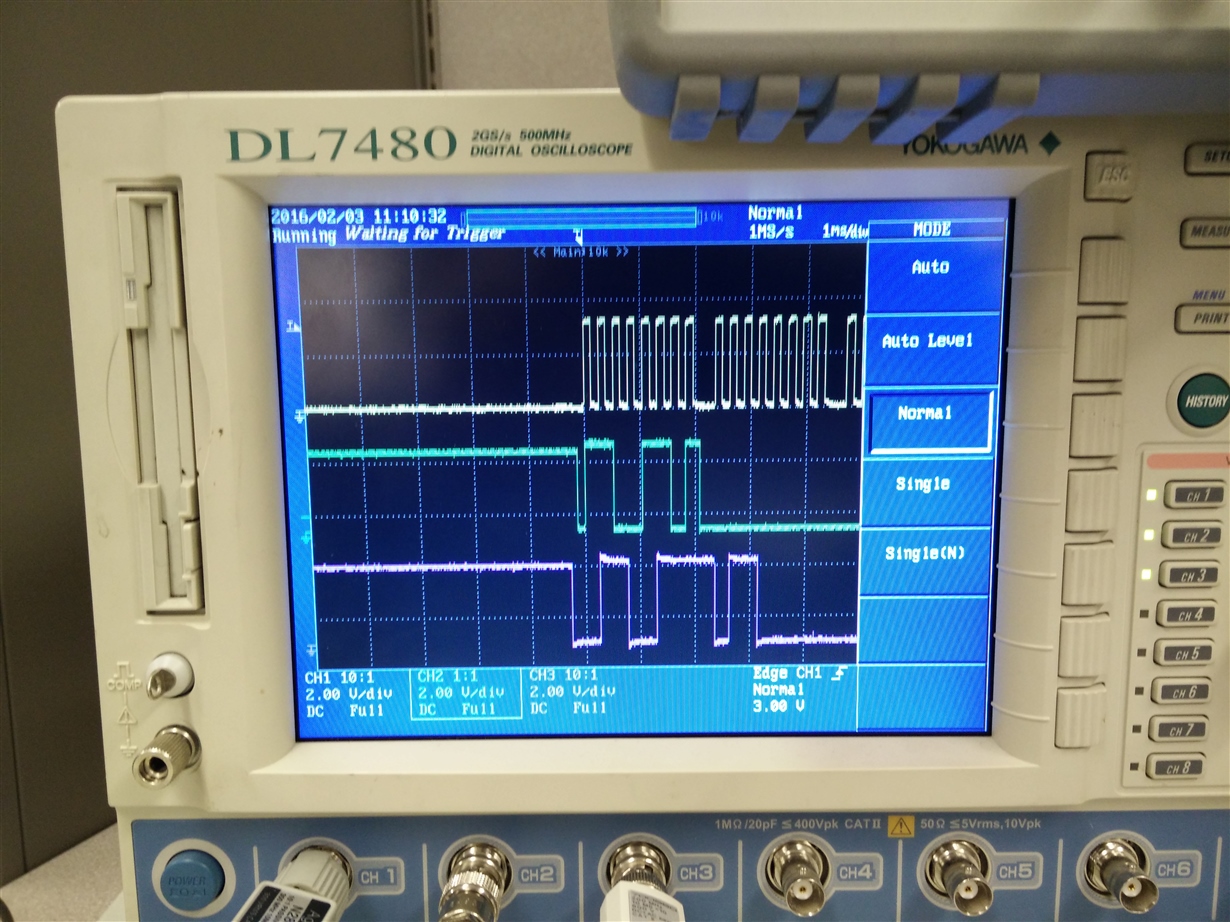

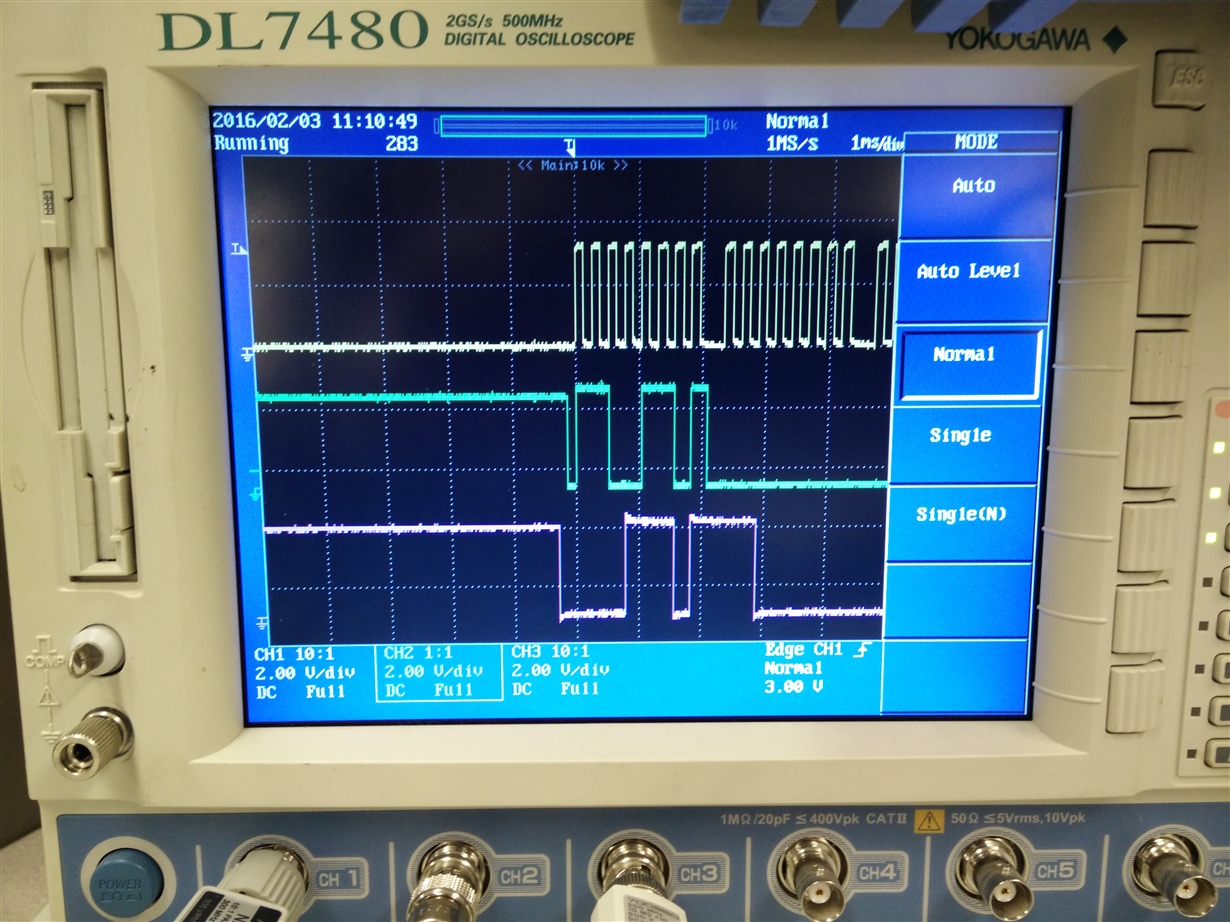

Attached a screenshot of DSO.

I am trying like this for quite long time now but get random data from AMC7812.

Thanks

Vitthal