Hi,

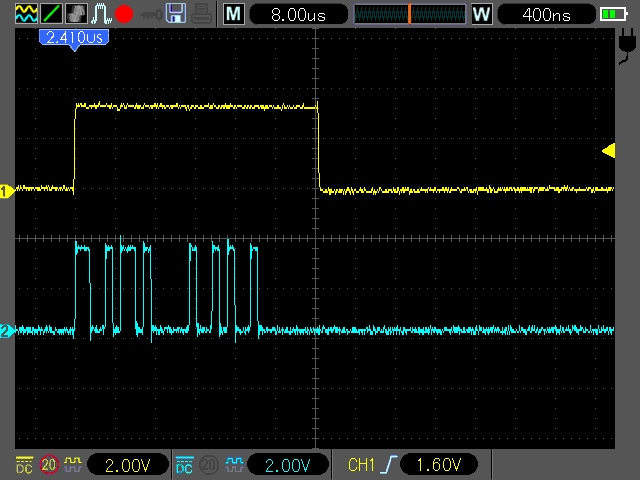

Years ago I developed an acquisition system based on ADS1278 and C6747 using this configuration:

- Frame-Sync format - Discrete DOUT mode

- High-Speed mode

- Discrete Data Output Mode

- CLK/SCLK range [11MHz to 18MHz]

- 8 input channels enabled

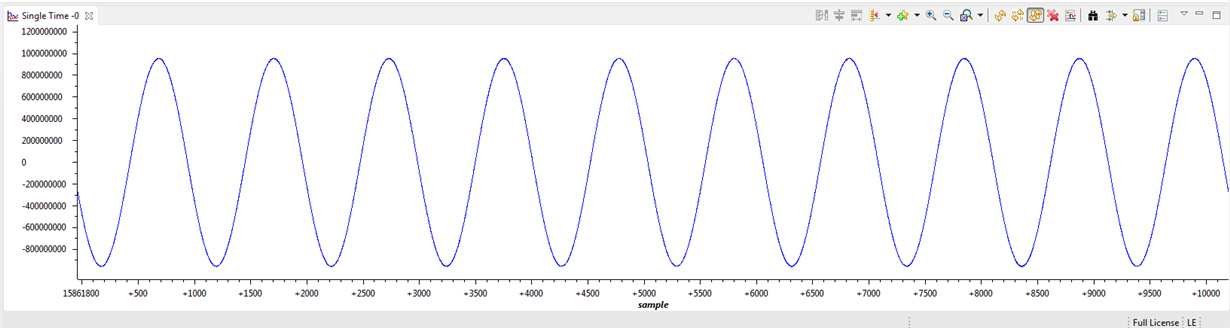

For each input channel, it was designed to acquire a low frequency sine waveform (40Hz to 70Hz) in 10240 samples through ADS1278 Frame-Sync Serial Interface and McASP+EDMA subsystem on the C6747. For example, the 10 cycles of a 50Hz input waveform comprises 10240 samples as shown (CLK/SCLK=13.107200MHz)

So far so good, 13.107200MHz / 256 = 51200SPS that fits with the expected results (51200SPS / 10240 samples = 5Hz, the window's size)

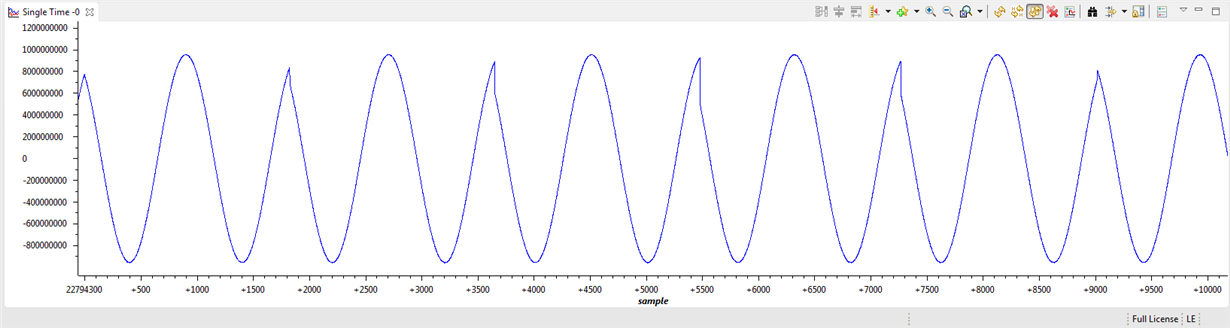

However, if I change the input frequency to 51Hz I get a distorted waveform (CLK/SCLK remains fixed to 13.107200MHz)

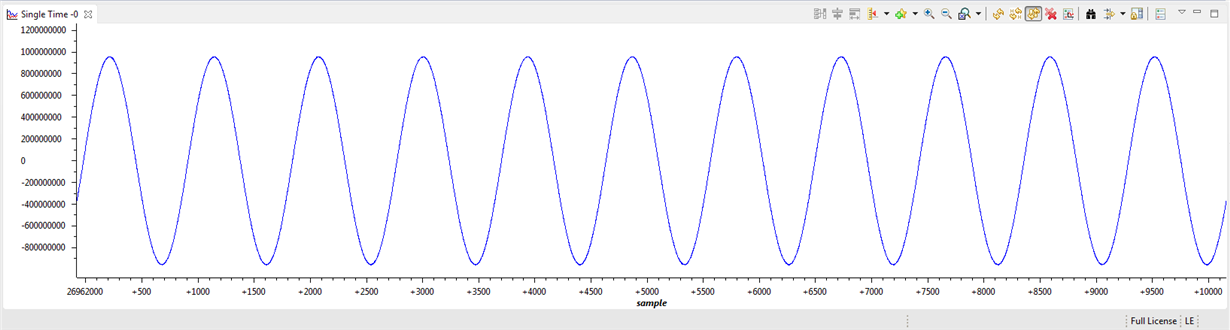

Now if I set the input frequency to 55Hz (a multiple of 5) everything is okay (noticed that we have 11 entire cycles instead 10)

It seems I cannot introduce an input waveform different of a multiple of 5Hz. Why? Can anybody explain me what's going on? I'd appreciate any help.

regards,

gaston