I don't have any problem with ADS131A04 except CRC function.

My ADS131A04 is set to

Asynchronous interrupt mode (M0, High)

32bit Device word length (M1, High)

Hamming code word validation OFF (M2, Low)

Dynamic Farme size

CRC mode 0

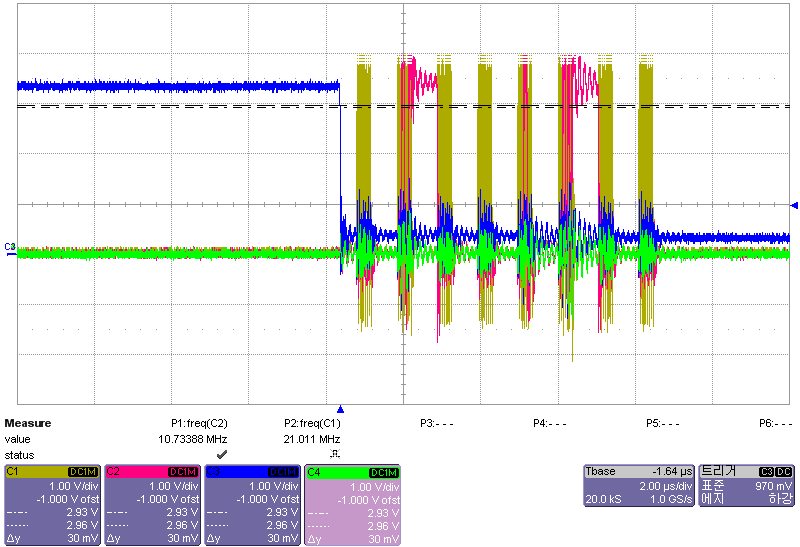

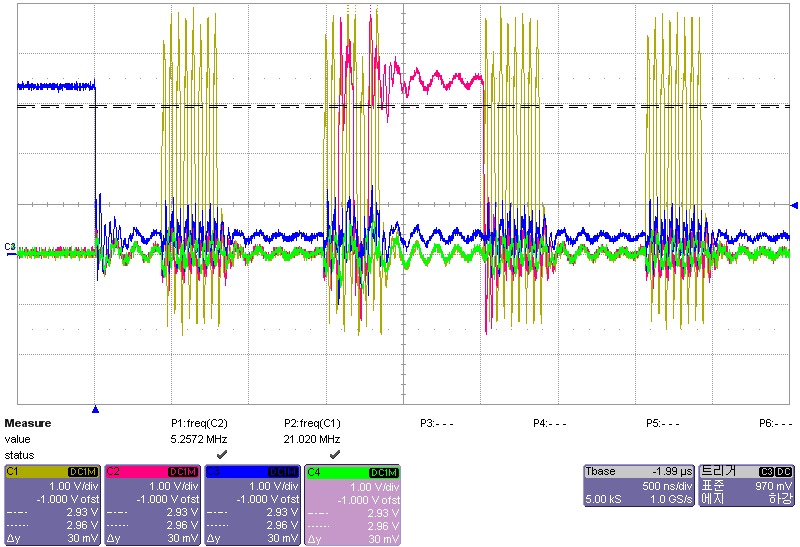

Here is my part of command sequence.

Command: 0x4C 3D 00 00 (WREG command for CRC enable), Response: 0x2E 4E 00 00 (0x0E resgister)

Command: 0x00 33 00 00 18 35 00 00(Wake up command with CRC word), Response: 0x2C 3D 00 00 00 00 00 00 (0x0C resgister)

Command: 0x05 55 00 00 8D BB 00 00(Lock command with CRC word), Response: 0x22 21 00 00 00 00 00 00 (0x02 resgister, Fault SPI & DIN check)

I calculated CRC value with On-line CRC calculator.

(CRC-CCITT, polynom is 0x1021, Initial value is 0xFFFF)

Does anyone know what the problem is?

Can I get command example with CRC word? or any advice?

Thank you for your attention.