I am using ADS8528 12 bits ADC. I test it with a 2 volts DC in to the A0. Other voltage levels in to other channels. hardware set to 2XVREF, using parallel interface and hardware set.

I am doing this.

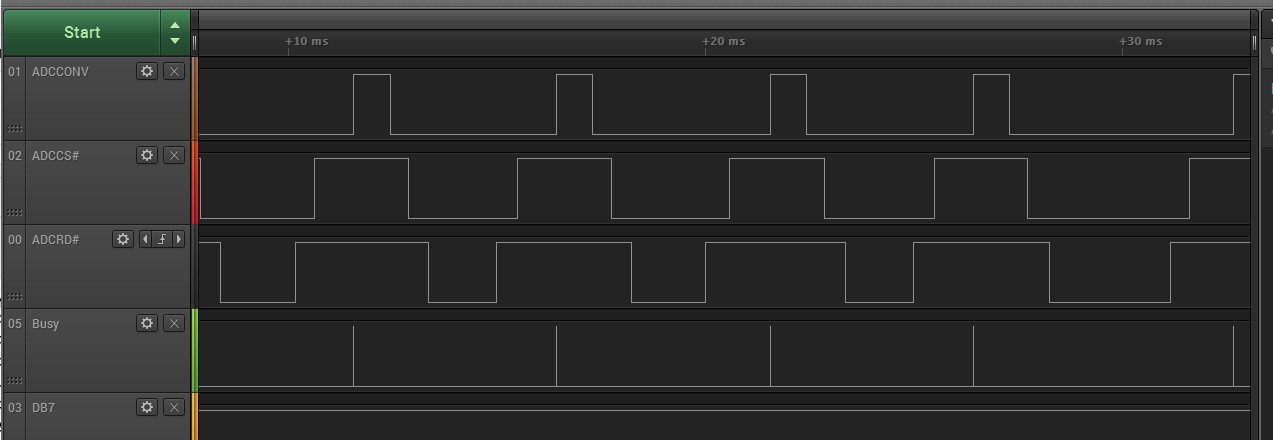

1. Toggle convert pins to high than low, pulse width is about 500 uSec.

2. activate CS#

3. toggle RD# and read data A0, than toggle RD# again to read other channels

4. deactivate CS#

Repeat step 1 to 4 again and loop continues

The data of A0 every time I read is different with huge different and can be +/- 0.7 volts

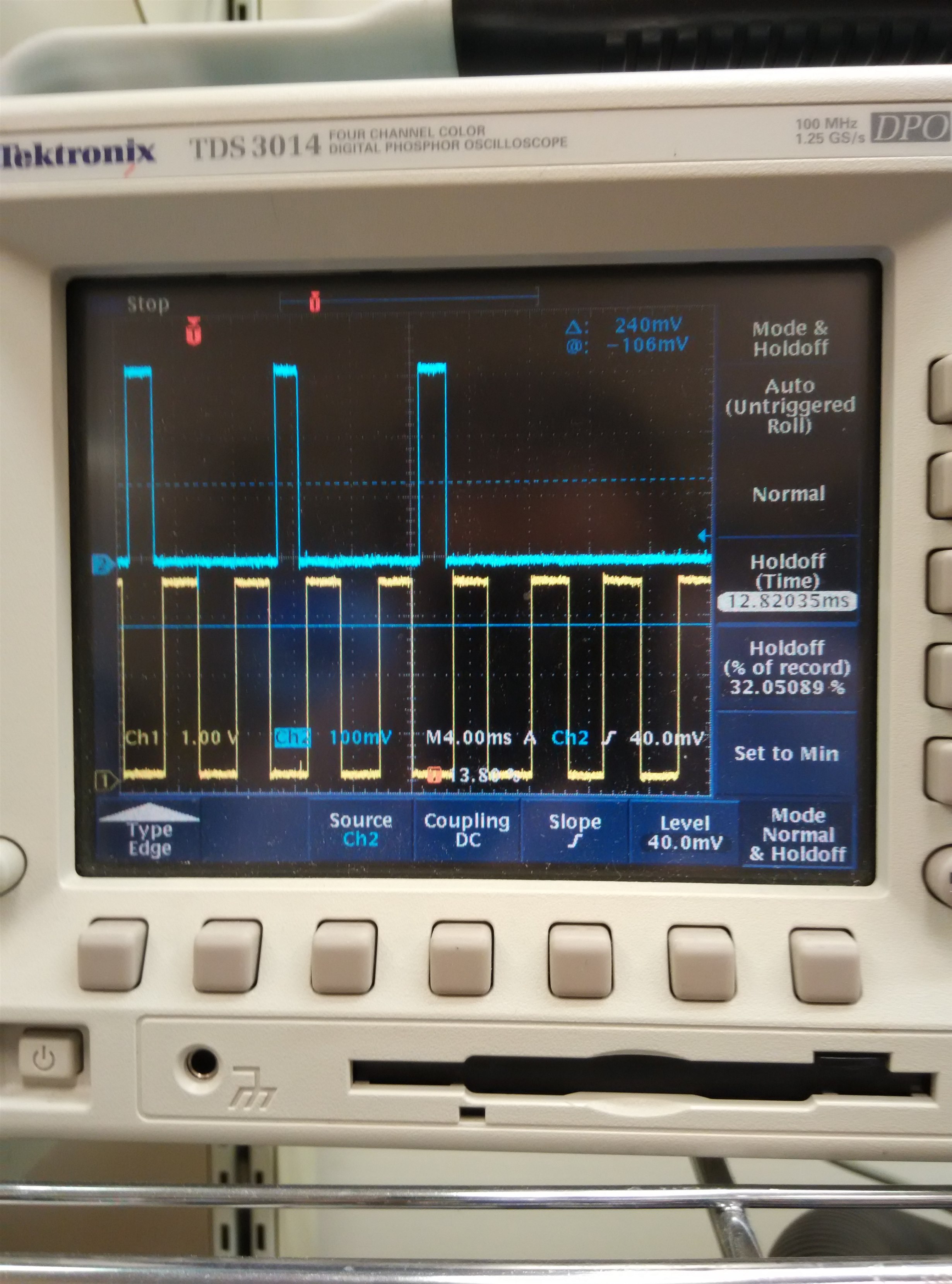

I checked the DC is good with about 50 mV noise on scope and is stable.

Any hints of what is my problem.

I am behind schedule very much already. Any quick help is appreciated. Thank you.

Rgds

kk chan