Hi,

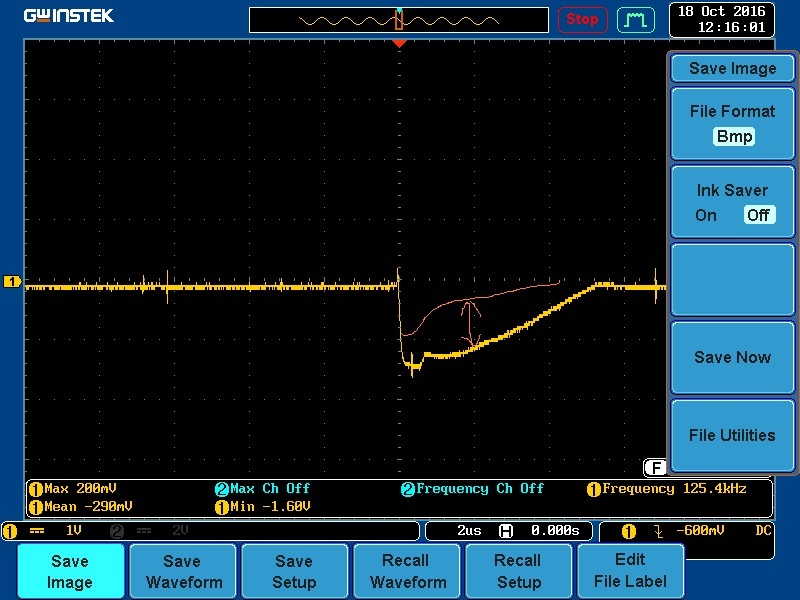

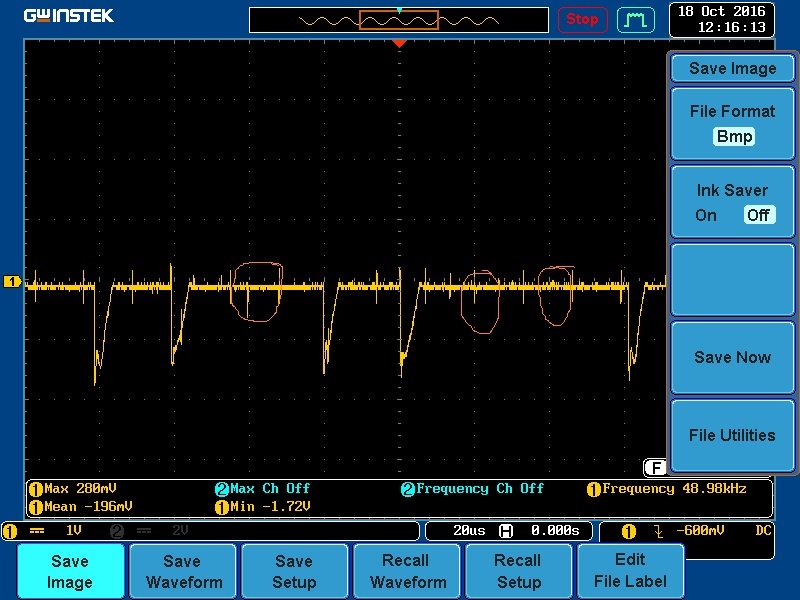

I test DAC8871 through SPI Interface @ 50M for an entire dynamic range of +10V to -10V.

As such the output follows the input digital code [driven by an FPGA].

But For digital code equivalent to 0V [8000] and +640mV and +1.25V , I find negative going voltage spikes [so much so from -500mV upto -2.5V.

Why it can be so? Can the timing failure of SPI be code selective or is it some other issue inherent to DAC?

Please help.