I'm trying to estimate the noise free resolution of the ADS1231 but can't seem to find the current noise of the PGA in the datasheet. I suppose the voltage noise is dominant for bridge circuits up to 1kOhm?

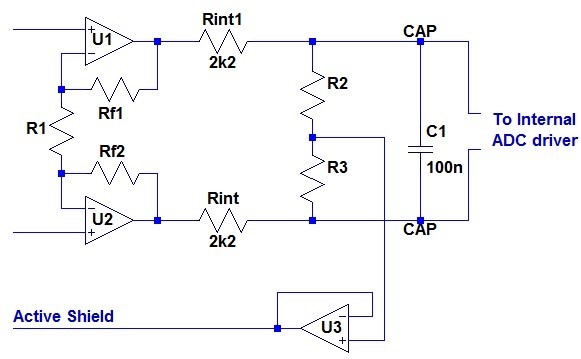

For my application a load cell with several meters cable needs to be measured with high resolution. The load cell cable runs parallel to noisy lines (pump and solenoids) therefore I plan on using on active shield. Would 2x 100k across the CAP pins followed by a low current noise/bias OPAMP as a shield driver cause any problems? The added gain error is no problem because this will be calibrated out.

Since I already plan on using x7r x2y capacitors for the input filter would it be a good idea to use them also on the CAP pins or would I be much better of using the suggested NP0 capacitor? The samples will also be filtered using software from 10sps to 1sps.

Thanks,

Koen