Hi all,

I'm having some problems with a TLV2548 not returning the correct data. To investigate this, I'm analysing the timing, especially around the SPI link in Mode 0, but struggling to understand the datasheet!

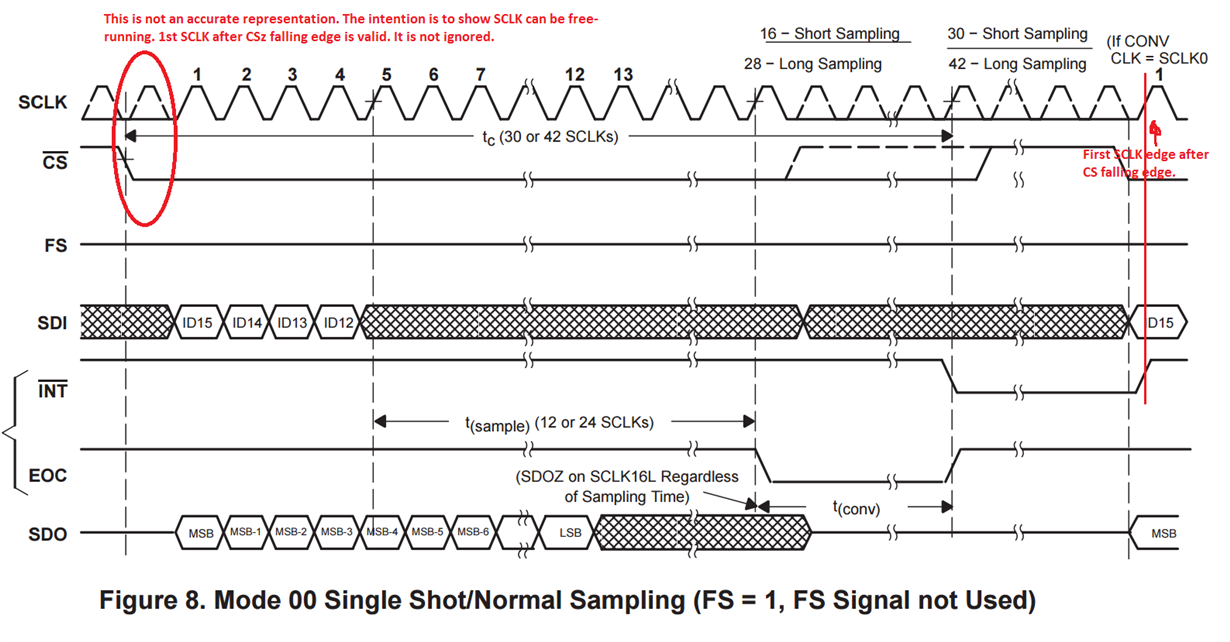

Figure 8 in the datasheet gives mode 0 operation (in my design FS and CSTART=1), but it seems to show a 1 SCLK timing delay between CS falling edge and the first SDI data being presented: is this correct, or a documentation artefact?

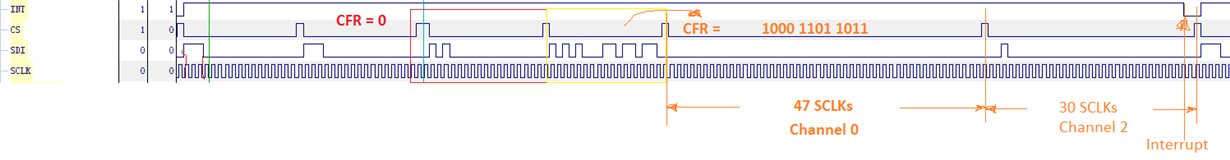

Also, the datasheet indicates a 42SCLK delay between readings, but again Figure 8 shows an additional delay after the 42 SCLKs before CS is raised. Does the overall SCLK timing needs to be a byte-multiplier (eg 48 SCLK)?

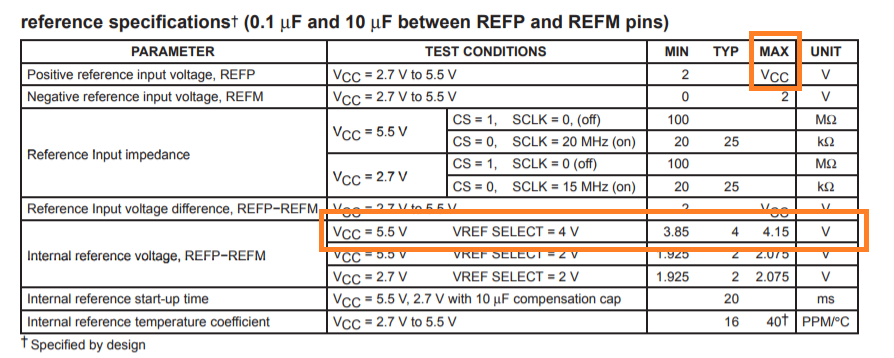

Any extra information on driving these chips at Mode 0 would be appreciated: I'm currently testing the chip using it's internal reference (div2), but returning millivolts range: it reeks of a 2bit-shift in the datastream somewhere!

cheers

Mat