Other Parts Discussed in Thread: OPA1632

Hi,

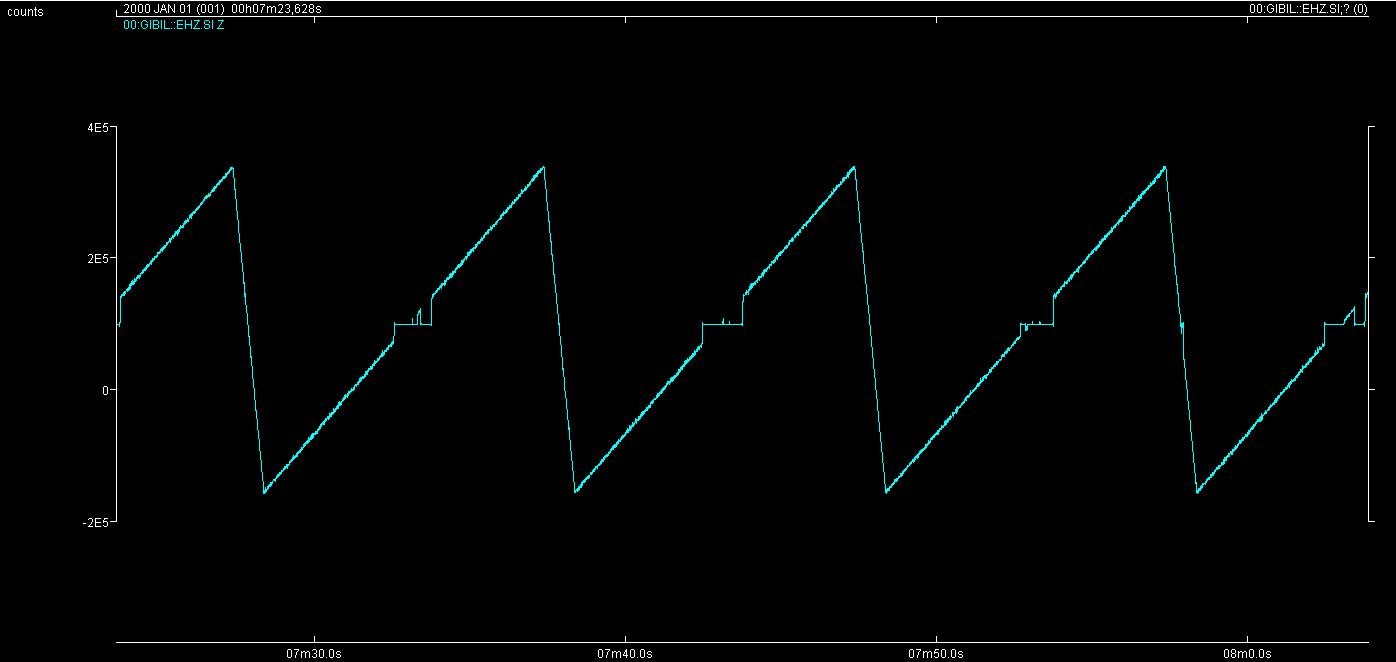

I am testing an ADS1281 with a triangular wave signal. My problem is that converted data show a strange type of distortion near zero. I connected oscilloscope probes to both inputs of the ADC and I saw regular triangular waves, without distortion. The sampling process lasts less than 1us, so I know that what I see on the oscilloscope is not what the ADC is measuring in reality. My guess is that the antialiasing filter causes this problem because of its high common mode impedance, but I do not know how.

Below you can find:

1. a screenshot of the oscilloscope (yellow = negative ADC input 2mV/div; blue = positive ADC input 2mV/div; pink = difference between positive and negative 1mV/div);

2. A picture showing converted data

3. A schematic view of antialiasing filter that shows a some details of the test setup.

My next step will be repeating the same test with another board that has an active anti-alising filter instead. If anyone can help with the passive filter case depicted above I would really appreciate it.

Regards, Gioacchino