Dears,

I occur some issue with PGA411, please help to give some advise.

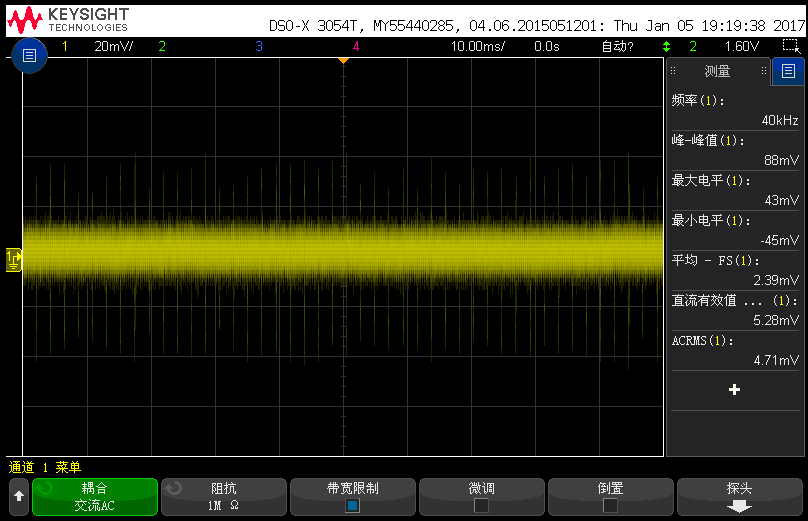

Issue 1: the ripple of the BOOST is too big.

We boost 6.5V to 12V to supply power to the VEXT. The ripple of input 6.5V is less than 100mV, while the output ripple is about 650mV .

Input ripple:

output ripple:

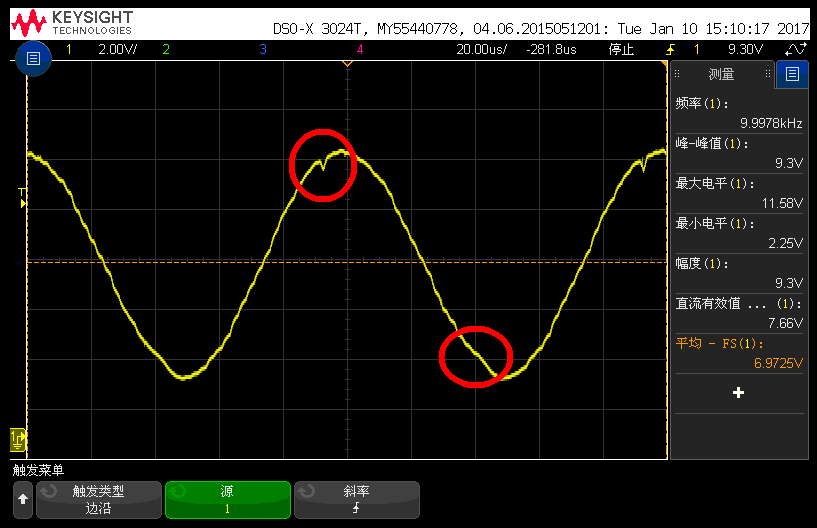

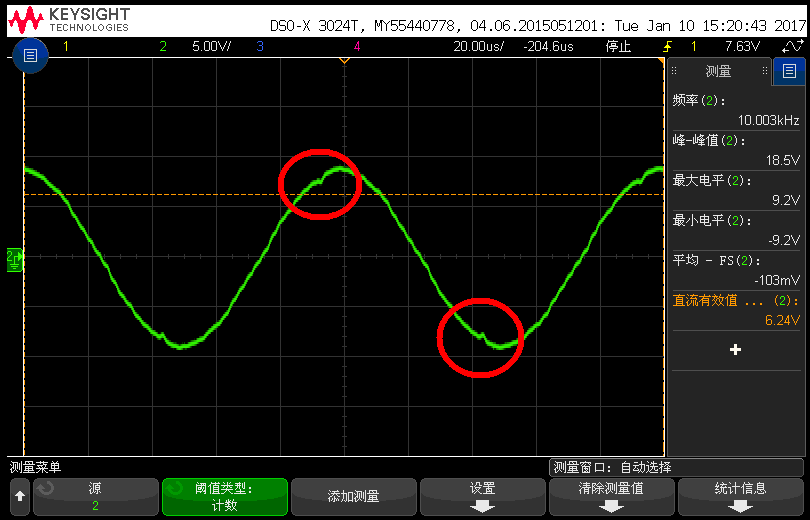

Issue 2: the output of the exciter-amplifier distorts.

As the graph below shows, there are two peaks in the red circle every cycle. And the sine degree of the wave is not good.

Wave of OE1:

Wave of OE(differential wave)

Issue 3: The FAULT pin will turn high without the resolver. the SFAULT of DEV_STAT4 is 1, while the other bit are all 0. So I can't get the Fault type.