Other Parts Discussed in Thread: LM7705, REF5050, OPA376, OPA727, DAC8811, THS4011, LM4050-N-Q1

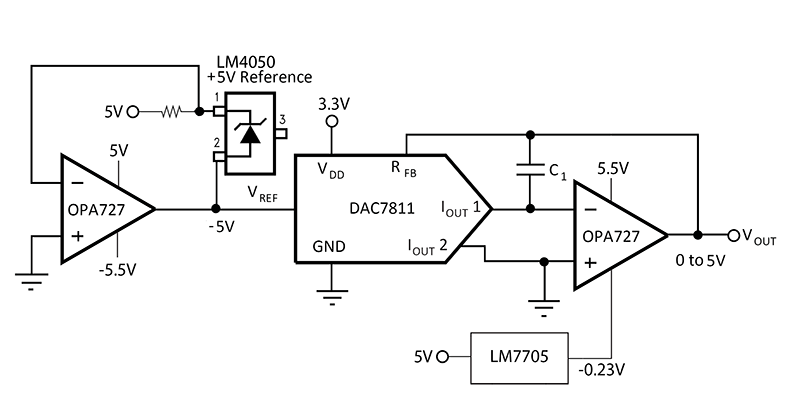

I need a 0 to 5V output from the DAC7811. I figured out a solution that I think will work, but I would appreciate it if someone would please review my schematic. I based it off of Figure 29 in the data sheet. I used an LM4050 5V reference since I am already using it in an existing product. If it isn't ideal I could use something else. The reason I included the LM7705 for the negative supply of the output op-amp is only because it made me feel better that the output would never go very far negative if the circuit failed. Maybe I'd be better off using the -5.5V supply and putting a Schottky diode clamp to ground on the output to prevent it from going too far negative. VDD of the DAC7811 is 3.3V because that is the interface voltage to the FPGA.

Here is the schematic:

Any advice would be greatly appreciated.

Greg